Broadwell (14 nm)

A Broadwell-alapú processzorok felépítésének alapját a megelőző generációs, 22 nm-es technológiával gyártott Haswell mikroarchitektúra adja, amelyet néhány ponton csiszoltak, kisebb módosításokat végeztek rajta:

- 60-ról 64 eleműre bővül az out-of-order ütemező mérete;

- másfélszeresére, azaz 1536 eleműre nő a másodszintű TLB (virtuális -> fizikai címfordítást végző/gyorsító egység) mérete a 4 kB-os és 2 MB-os lapokra, és új, 16 elemű TLB-t kapnak az 1 GB-os lapok;

- ugyancsak a címfordítást gyorsítja a bevetett második címfordító, melynek segítségével két címfordítás végezhető párhuzamosan, amennyiben azokra nincs találat a gyorstárban;

- az indirekt ugrások címét megjósoló prediktor munkaterülete nő.

A fenti változások mellett nagyobb mértékű fejlesztések érintik a lebegőpontos számítások végrehajtását:

- a szorzások végrehajtási időidénye 5 órajelről 3 órajelre csökken, így immár ugyanannyi, mint a lebegőpontos összeadásé/kivonásé;

- az osztások gyorsítását szolgálja az 1024 Radix osztómű, amely lehetővé teszi 2,5 órajelenként új egyszeres vagy 4 órajelenként új dupla pontosságú osztás kiszámításának elindítását.

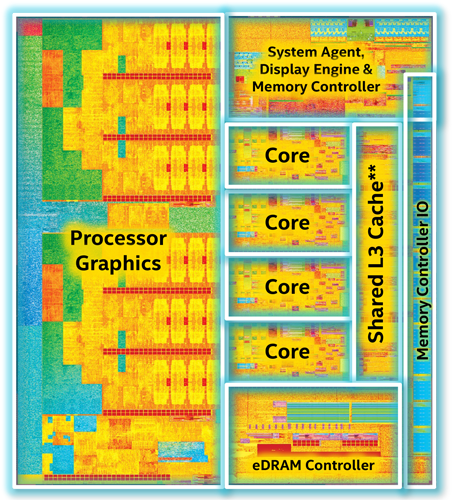

A négymagos Broadwell (GT3e) lapka felépítése [+]

Ugyancsak jelentős, körülbelül 60%-os sebességelőnyre tesznek szert a Haswellben bevezetett gather memóriaolvasások.

Fejlesztések történtek a titkosítási/biztonsági algoritmusokat érintően is:

- az ADC (ADd with Carry: x=x+y+Carry Flag) és SBB (SuBtract with Borrow: x=x-y-Carry Flag) utasítások végrehajtása gyorsul;

- új utasításként bemutatkozik az ADCX és ADOX, amelyek az ADC-hez eltérően csak 1 flaget (az előbbi a Carry-t, utóbbi az Overflow-t) módosít, ebből veszi, illetve ebbe helyezi a túlcsordulást, így párhuzamosan két utasításlánc hajtható végre belőlük;

- gyorsult a számos hash/CRC algoritmusban használt PCLMULQDQ utasítás végrehajtása;

- ugyancsak új utasítás a nem determinisztikus random számok generálására alkalmas RDSEED.

Újdonság továbbá az Ivy Bridge-ben bevezetett SMEP védelem párja, az SMAP (Supervisor Mode Access Protection): ennek aktiválásakor a kernel módban futó programkód nemcsak hogy nem hívhat meg felhasználói módú programrészt – ezt akadályozza meg az SMEP –, hanem felhasználó által hozzáférhető/módosítható adatterületről nem is olvashat be adatot.

Az F0 steppinges Broadwell processzoroktól kezdődően ismét elérhetővé vált a Haswell esetében bevezetett, majd később letiltott TSX (tranzakcionális memóriakezelés). Emellett a virtualizációs, valamint az imént említett tranzakcionális memóriakezelést biztosító utasítások végrehajtását is módosították; utóbbi elsősorban nagyobb lehetséges tranzakcióméretben nyilvánul meg.

A cikk még nem ért véget, kérlek, lapozz!