A Haswell

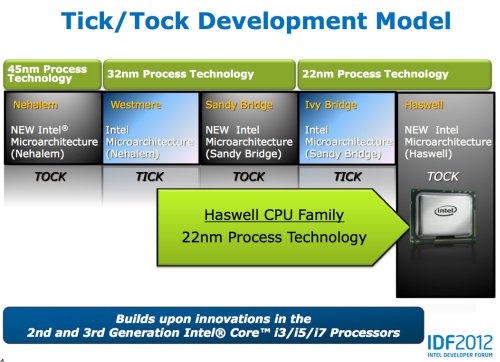

A Intel tick-tock elve szerint új gyártástechnológia bevezetésekor először a már meglévő, aktuális mikroarchitektúrára alkalmazzák azt, mely elsősorban gazdaságosabb gyártást eredményez. Ezen termékvonal felfuttatása elegendő időt biztosít a tervezőcsapatok számára, hogy a csíkszélesség csökkentésével előálló, a gazdaságosan gyártható lapkaméretbe beleférő többlet tranzisztormennyiséget a következő mikroarchitektúrában átgondoltan költsék el.

A "tick" lépcső keretein belül debütált Ivy Bridge tavaly április végén elhozta a 22 nanométeres csíkszélességet, melyen azt megelőzően több mint egy évtizedet munkálkodott az óriásvállalat. Kissé rendhagyó módon mikroarchitekturális változásokat is eszközölt az Intel, melyről korábbi elemzésünkben részletesen beszámoltunk. Ezzel CPU oldalon 3-8% javulást ért el az Ivy Bridge, míg az integrált GPU tekintetében a korábbi HD Graphics 3000-hez képest durván 30%-ot gyorsult a HD 4000-es IGP. Bár utóbbi jelentős mértékű előrelépésnek számított, bizonyos esetekben még mindig nem volt elég a konkurens csúcs AMD APU-k grafikus teljesítményének beéréséhez, vagy éppen felülmúlásához.

Utóbbi okán nem is lehetett kérdés, hogy a következő generáció egyik célkitűzése az integrált grafikus mag képességeinek további javítása lesz. Ezzel párhuzamosan az x86-os CPU magok tempójának javítása sem kerülhetett le napirendről, hiszen ez a "tock" lépcső egyik kötelező eleme. Az Intel részéről a Haswell azonban sokkal többről szól, mint a termékkategória puszta frissítéséről: üzleti szempontból az új architektúrának igen komoly küldetése van. Ebből az aspektusból társoldalunk, az IT café cikke foglalkozik az újdonsággal.

Hirdetés

A Haswell lapka

Haswell és Ivy Brige [+]

(nem méretarányos)

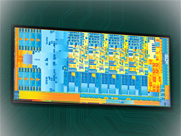

A fenti, négymagos lapkákat ábrázoló képekből megállapíthatjuk, hogy az új lapka alapvető felépítése a Sandy Bridge által lerakott "soros" elrendezést követi. A két dizájnt összehasonlítva láthatjuk, hogy tovább hízott a grafikus szekció, illetve a jobb szélen látható "System Agent" kezdetű terület is megnőtt. Ennek egyik oka, hogy immáron a digitális kijelzők interfésze az alaplapi chipkészletből (PCH) beköltözött a processzorba. Ahogy már utaltunk rá, a gyártástechnológia nem változott, ergo maradt a tavaly debütált 22 nm-es Tri-Gate technológia.

Itt még az alaplapon [+]

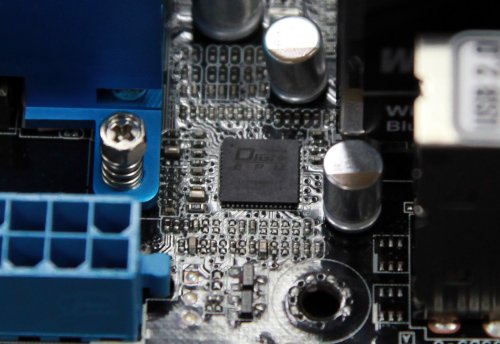

A Haswell lapka második új lakója a feszültségszabályzó kis chip (voltage regulator), mely korábban valahol a CPU-foglalat közelében volt megtalálható, és annak típusáról az alaplap tervezője gondoskodott. Ennek kiviteléről és ezzel együtt képességeiről mostantól az Intel gondoskodik. Ezzel ismét egy komponenssel kevesebb kerül fel az alaplapokra, ami a gyártási költségekre, illetve a szükséges területre minden bizonnyal jó hatással van, ugyanakkor az alaplapok tervezőinek kezét kissé megkötheti.

iVR: integrated Voltage Regulator [+]

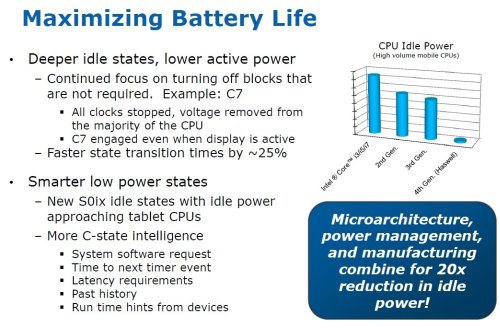

Pozitív hozomány, hogy az Intel mostantól pontosan tudja, mire képes a vezérlő, így ő magabiztosabban építkezhet rá, nem kell tartania esetleges kompatibilitási vagy képességbeli problémáktól. Minden bizonnyal ezen újításnak köszönhető, hogy újabb energiatakarékossági módokkal gazdagodott a Haswell.

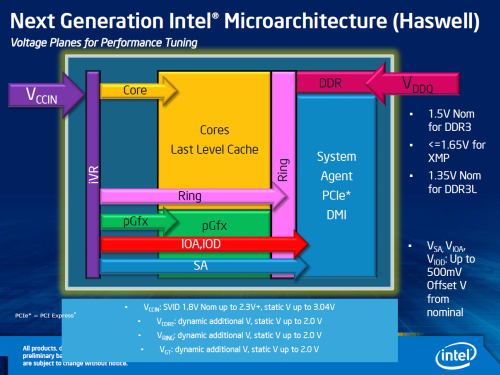

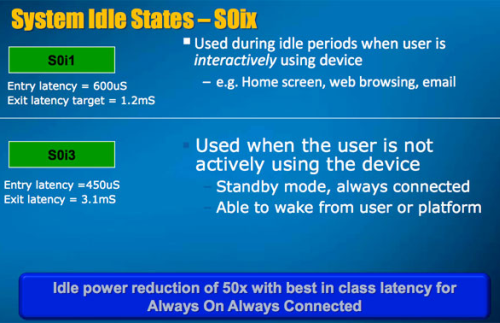

A fenti ábrán látható S0i1 és S0i3 módokon felül megjelentek a C6 és C7 jelzésű energiatakarékossági szintek is, bár előbbieket csak az Y és U szériás mobil megoldások estében lesznek aktívak.

Az újabb módokkal alacsony terhelés vagy teljes üresjárat mellett további wattok takaríthatóak meg. Mint azt már korábban elmondtuk, az Intel elmúlt néhány processzorcsaládja már elsősorban az akkumulátorokról üzemelő, mobil gépek igényeinek megfelelően került kialakításra, itt pedig minden egyes megspórolt watt sok perces üzemidőt jelenthet. Ennek ellenére természetesen asztali környezetben is használhatóak az új módok, melyek közül a C7-hez már olyan tápegység szükséges, ami a rendkívül csekély, 0,05 ampert is képes stabil feszültség mellett biztosítani.

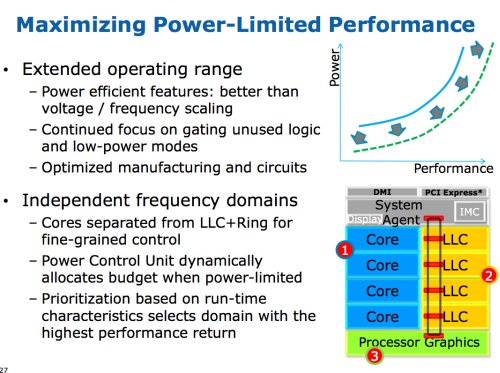

További említésre érdemes különbség, hogy visszatért a Nehalem esetében már látott, úgynevezett "Uncore" (vagy "Ring") órajel. Ez elsősorban az L3 cache, illetve az azon keresztül futó körbusz órajelét takarja. A Sandy, illetve Ivy Bridge esetében ez a szekció a CPU-magok mindenkori órajelén futott, de a tervezők a Haswell-lel ismét kettéválaszották az egyes üzemi frekvenciákat. Ezzel a magoktól eltérő órajelen futtatható a meglehetősen méretes L3 cache (is), amivel további energia takarítható meg. Egy lehetséges további előny, hogy a GPU az esetlegesen alvó x86-os magok órajelétől függetlenül igényelhet gyorsabb cache-t (magasabb órajelet), mivel mostantól a gyorsítótár különálló frekvencián üzemel. Mint sok minden másnak, ennek is megvan a hatránya, ugyanis ezzel a CPU-magok oldaláról megnőtt az L3 cache hozzáférési ideje, ami bizonyos esetekben negatívan befolyásolhatja a végrehajtás tempóját.

| Lapka kódneve | Gyártástechnológia | Magok száma | L2 + L3 mérete | Tranzisztorszám | Lapka területe |

|---|---|---|---|---|---|

| Haswell | 22 nm Tri-Gate | 4 (+ IGP) | 9 MB | 1,4 milliárd | 177 mm2 |

| Ivy Bridge | 22 nm Tri-Gate | 4 (+ IGP) | 9 MB | 1,48 milliárd | 160 mm2 |

| Sandy Bridge | 32 nm HKMG | 4 (+ IGP) | 9 MB | 995 millió | 216 mm2 |

| Sandy Bridge-E | 32 nm HKMG | 6 | 16,5 MB | 2,27 milliárd | 435 mm2 |

| Gulftown | 32 nm HKMG | 6 | 13,5 MB | 1,17 milliárd | 240 mm2 |

| Lynnfield | 45 nm HKMG | 4 | 9 MB | 774 millió | 296 mm2 |

| Bloomfield | 45 nm HKMG | 4 | 9 MB | 731 millió | 263 mm2 |

| Trinity | 32 nm HKMG SOI | 4 (+ IGP) | 4 MB | 1,303 milliárd | 246 mm2 |

| Llano | 32 nm HKMG SOI | 4 (+ IGP) | 4 MB | 1,45 milliárd | 228 mm2 |

| Orochi/Vishera | 32 nm HKMG SOI | 8 (4 modul) | 16 MB | ~1,2 milliárd | 315 mm2 |

| Thuban | 45 nm SOI | 6 | 9 MB | 904 millió | 346 mm2 |

| Deneb | 45 nm SOI | 4 | 8 MB | 758 millió | 258 mm2 |

A lapkához visszakanyarodva, a fenti táblázatból láthatjuk, hogy annak területe csupán minimálisan, 17 négyzetmilliméterrel nőtt, míg ugyancsak az Intel által szolgálatott adatok alapján a tranzisztorszám csökkent.

Haswell lapkák egy 300 mm átmérőjű ostyán [+]

A cikk még nem ért véget, kérlek, lapozz!