ASC, SMA, IPC

Intel Advanced Smart Cache

Az Advanced Smart Cache (továbbfejlesztett intelligens gyorsítótár) nem más, mint a Core processzorokban található megosztott, továbbfejlesztett gyorsítótár "beceneve". Intelligens (smart) elnevezését annak köszönheti, hogy a Core-ban a másodlagos gyorsítótáron a két processzormag megosztozik. Az Intel úgy fejlesztette ki az L2 cache-t, hogy ahhoz a két mag bármikor hozzáférjen, tehát a Core esetében már nem a rendszerbuszt terheli a két cache közötti adatforgalom. Ez a megoldás egyrészt csökkenti az adatokhoz való hozzáférés idejét (csökkenti a késleltetést), csökkenti a cache-koherencia szűréséből adódó adatforgalom mértékét (tehát nagyobb sávszélesség marad a hasznos adatok számára), másrészt hatékonyabbá teszi a helykihasználást, hiszen nem kell duplikálni az adatokat ahhoz, hogy mindkét processzormag számára elérhető legyen. A Core processzorok modelltől függően összesen 2 vagy 4 MB L2 cache-en osztoznak, ezt a végrehajtó egységek dinamikusan osztják fel egymás között, tehát erősen többszálú alkalmazások esetében a fentebb vázolt pozitívumokban részesülünk, a gyorsítótár attól függően kerül felosztásra, hogy az egyes végrehajtó egységek milyen gyakran szeretnének hozzáférni a gyorsítótárban található adatokhoz. Ugyanakkor az egyszálon végrehajtott alkalmazások során az egyik processzormag abban a megtiszteltetésben részesülhet, hogy egyedüliként használhatja akár az egész másodszintű gyorsítótárat (ha a másiknak éppen nincs rá szüksége).

Intel Smart Memory Access

A Smart Memory Access (intelligens memóriaelérés) égisze alatt két új technológiával ismerkedhetünk meg. Az egyik az Advanced Pre-fetch, amely továbbfejlesztett előbehívást jelent. A prefetcherek detektálják az alkalmazások adatmozgatási sémáit, és a gyakran igényelt adatokat gyorsabban elérhetővé teszik (beteszik a cache-be), ezzel csökkentve a memóriakésleltetést. A Core processzorokban összesen 8 prefetcher található (magonként 4), 2-2 db az L1 (ezek képesek szimultán több sémát is kezelni) és L2 (magonként több sémát is képesek követni) gyorsítótárban. A prefetcherek folyamatosan figyelik, hogy mikor milyen adatokra van szükség, és ennek megfelelően irányítják az adatforgalmat.

Az Advanced Pre-fetchen kívül a Smart Memory Access-t egy továbbfejlesztett Memory Disambiguation (egyértelműsítés) nevezetű technológiával is felvértezték, amely a soron kívüli (out-of-order) algoritmusok írási és olvasási hatékonyságát próbálja meg növelni azáltal, hogy a LOAD műveleteket a STORE-ok elé helyezi (lényegében a memóriaműveleteket újrarendezik a gyorsabb végrehajtás érdekében). Erre azért van szükség, mert nem lehet tudni, hogy az egymást követő LOAD és STORE műveletek függenek-e egymástól (azaz ugyanazon memóriacímre/regiszterre/stb. hivatkoznak-e). A Core architektúra elődeihez mérten akár 30-40%-kal is gyorsabb lehet abban az esetben, ha az algoritmus jól "jósolt", és az adatok közötti függőségben ez a "kavar" nem okoz galibát később (vagyis a LOAD utasítással előretöltött adattól a később meghívásra kerülő STORE nem függ). Ha viszont a művelet nem végződik sikeresen, a Memory Disambiguation detektálja a problémát, visszatölti az eredeti adatokat és újraindítja a kódot.

A Memory Disambiguation nem önmagában fejti ki csodálatos hatását, hanem a Core processzorok továbbfejlesztett előbehívóival (Advanced Pre-fetch) karöltve alkot egy komolyan előremutató újítást, utóbbi ugyanis képes előre megjósolni, hogy milyen adatokra lesz szükség a későbbiekben, ami pont kapóra jön a Memory Disambiguation számára. Ez a páros jelentősen képes növelni a processzor és a memória közti kommunikáció hatékonyságát (később látni fogjuk).

Intel Intelligent Power Capability

Az IIPC (intelligens energia-vezérlés) olyan tulajdonságok gyűjtőneve, melyek a hőtermelés kordában tartásáért felelősek.

- Ultra fine-grained Power Control (precíz energiavezérlés): a processzormagok kihasználatlan részei egyszerűen leállhatnak, miközben a mag más részei még dolgoznak. Itt nem az egész magról van szó, hanem annak egyes részeiről!

- Split Buses: a processzormagok és a belső adatbuszok feloszthatóak több kisebb részegységre, melyeket így egymástól elkülönülve tud vezérelni (ki-be kapcsolni) egy vezérlőáramkör.

- Platformization of Power Management Architecture, három részből tevődik össze:

- PSI-2 vagyis Power Status Indicator (mobil CPU-k): a processzor jelzi a rendszer felé a terhelést, így együttesen képesek optimalizálni a feszültségszabályzó áramkör és a leadott teljesítmény hatékonysági mutatóit.

- DTS (Digital Thermal Sensor): a processzorban immár nem egy, hanem több hőszenzor található, melyek a processzor minden egyes részén külön-külön felügyelik a hőmérsékletet, ezzel a precíz mérési metódussal pedig tovább tökéletesíthetőek a különböző hőmérsékletszabályozási sémák (az alaplapgyártókon sok múlik).

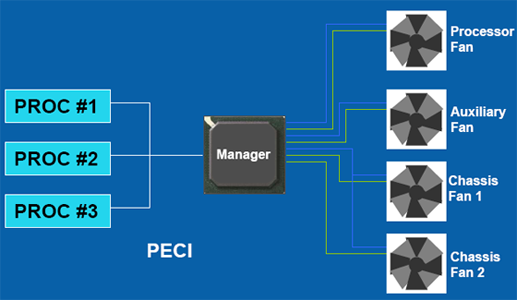

- PECI Interface (Platform Environment Control): a processzor képes egy külön erre a célra tervezett chipen keresztül a hőmérséklettől függően szabályozni a rendszer többi elemét is (ventilátorok).

A cikk még nem ért véget, kérlek, lapozz!