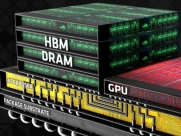

A HBM memóriaszabvány az idei Hot Chips rendezvény alkalmával főszerepbe került, ugyanis ez lehet az alapja az iparág további fejlődésének, miután a hagyományos memóriastruktúrákkal már nem lehet értékelhető fogyasztás mellett növelni a teljesítményt. A Hynix és az AMD által közösen kifejlesztett HBM memóriaszabványnak már a második generációs változatai is rendelhetők, amelynek a specifikációit korábban véglegesítette a JEDEC. Bár hivatalosan nem HBM2 a neve, a Hynix és a Samsung is így utal rá, vagyis gyakorlatilag használható ez a jelölési forma.

Hirdetés

A Hot Chips alkalmával a Hynix továbbra is arra a tervre koncentrál, amelynek keretében mindenhova HBM-et kínálnának. Ennek megfelelően be is mutatták a teljes HBM2-es flottát:

A képről látható, hogy 8, 4 és 2 GB-os szettek érhetők el, amelyek 1024 bites buszt használnak. Ezek a szettek rendre 8Hi, 4Hi és 2Hi kiépítésűek, vagyis 8, 4 és 2 darab, 8 gigabites memória lesz egymásra tokozva. Hivatalosan egyébként mindegyik memória támogatja az ECC-t, vagyis a valós kapacitásuk nagyobb a kihasználhatónál, de az extra tárhely kizárólag az ECC-nek van fenntartva.

A Hynix szerint van már 4 gigabites memóriájuk is, így azokat is képesek egymásra tokozni a fentiekhez hasonló módon, ugyanakkor a ma elérhető csomagok csak 8 gigabites memóriákat használnak, és az igények alapján dönt a cég arról, hogy milyen 4 gigabites memóriákra épülő HBM csomagok lesznek. Ez a Hot Chips rendezvényen egy felhívás is a potenciális partnerek felé, hogy jelezzék az igényeiket, ugyanis sokféle konfigurációt lehet építeni, de még nem teljesen tiszta, hogy mire lesz szükség.

A Hynix memóriái egyébként 1, 1,6 és 2 GHz-es órajelen üzemelhetnek, vagyis rendre 128, 204 és 256 GB/s-os tempóra képesek.

A Samsung a témát egy kicsit más oldalról közelítette meg. Egyrészt a cég is kínál majd hasonló HBM csomagokat, de ugyanakkor már fejlesztenek egy csökkentett I/O kiépítésű megoldást is. A HBM csomagok esetében ugyanis nem feltétlenül szükséges 1024 bites buszt alkalmazni. Elsődlegesen azért használnak ennyit, mert így a legjobb az energiahatékonyság. Ugyanakkor a HBM annyival a többi konstrukció előtt jár, hogy egy kevés hatékonyság fel is áldozható a költségek csökkentése érdekében.

Samsung Low Cost HBM konstrukció [+]

Az 512 tűs, vagy ehhez hasonló I/O konfiguráció csökkentené az interposer bonyolultságát, illetve a Samsung véleménye szerint eltávolítható lenne a pufferezésre szolgáló lapka is, ahogy az ECC-re sincs feltétlenül szükség. Ilyen formában jelentősen redukálható a HBM bevetésének költsége, így olyan piacok is megcélozhatók lennének, ahol a HBM jelenleg még tabu.

A Samsung szerint az úgynevezett Low Cost HBM ~512 bites I/O kiépítéssel ~3 GHz körüli effektív órajelen már nagyjából 200 GB/s-os tempót tudna. Persze a fogyasztása nagyobb lenne, mint a 2 GHz-es 1024 bites variánsé, de olcsóbb lenne implementálni az adott partner számára. És itt ki kell emelni, hogy a fogyasztás még így is sokkal-sokkal jobb, mint amire egy DDR4, GDDR5 vagy GDDR5X konfiguráció képes lenne hasonló adatátviteli tempó mellett.

A harmadik generációs HBM is szóba került már, amit az érintettek nem túl meglepő módon HBM3-nak neveznek. Ennek az egyik célja a költségek általános csökkentése, de úgy, hogy közben a fogyasztás is csökkenjen, miközben az adatátviteli tempó növekedjen. Egy HBM3 csomag esetében 512 GB/s-os tempó lesz a cél, de a részletekről sajnos még nincs pontos adat. A HBM3 valamikor az évtized vége előtt jöhet.