Út a HBM-hez

Az AMD a mai napon hivatalosan is bemutatta a HBM memóriaszabványt, amelyről a vállalat nemrég egy zárt konferencián tájékoztatta a médiát. A HBM-ről a lapunk hasábjain már viszonylag sokat írtunk, hiszen többek között a Hynix az idei CeBIT-en mutatta meg magát a memóriát, illetve arról is régóta tudni, hogy a két cég közösen fejezte be a fejlesztést mindenki mást kizárva az első generációs verzióból.

Hirdetés

Magán a konferencián Joe Macri, az AMD technológiai igazgatója beszélt a HBM megszületéséről, illetve előnyeiről, továbbá az is kiderült, hogy egy közel hétéves fejlesztésről van szó. Bár magát a HBM koncepcióját nem Joe Macri találta ki, a szakember vezető szerepet vállalt a fejlesztésben és később a szabványosításban, hiszen ez a JEDEC vezető beosztású tagjaként a kötelessége.

Joe Macri elmondása szerint az AMD 2007-ben figyelt fel arra a trendre, amelyre egyébként a GDDR5-tel akkor már bőszen kísérletező memóriagyártók is felkapták a fejüket. Ez az AMD számára nem volt nehéz, hiszen a GDDR5 fejlesztésében is vezető szerepet vállalt a cég, így az első kísérleteket az akkor még tervezés alatt álló RV770 kódnevű grafikus vezérlővel már el lehetett végezni.

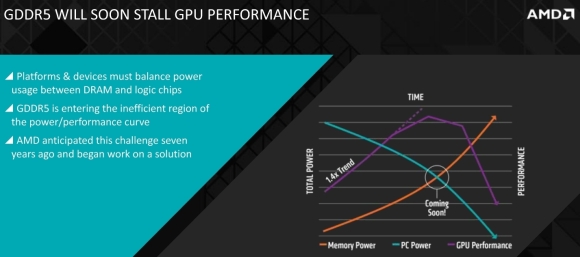

A GDDR5 egyik nagy problémája az volt, hogy a DDR3-nál lényegesen több energiát igényelt, és itt nem feltétlenül magukra a memóriákra kell gondolni, hanem a memóriák működtetéséhez szükséges teljes konstrukcióra, ideértve a memóriavezérlőt, valamint a GDDR5 lapkák működéséhez szükséges egyéb komponenseket. Ráadásul a fogyasztás a GDDR5 memóriák órajelének, illetve az üzemfeszültségének növelésével csak rosszabb lett, így elértünk arra a pontra, hogy egy 300 wattos TDP fogyasztással rendelkező csúcskártyán a GDDR5 memóriák, illetve a működésükhöz szükséges komponensek elviszik a fogyasztási keret majdnem egyötödét. Ez azt is jelenti, hogy a VGA-kra kisebb fogyasztású GPU-kat lehet építeni, és ez a trend az elmúlt években nagyon is megfigyelhető volt.

A legfőbb probléma, hogy mára nagyon közel kerültünk ahhoz a ponthoz, amikor a teljes memória-alrendszer már többet fog fogyasztani, mint maga a grafikus processzor, és ekkor a VGA-k teljesítménye nem nőni, hanem csökkenni fog. Ennek az elkerülésére az AMD több koncepciót is felvetett hét éve. Az egyik a videomemória integrálása magába lapkába, amit nagyon gyorsan elvetettek, mert a DRAM erre nem ideális. A másik opció egy új, GDDR5 utáni DRAM memória volt, de az ezeknél a koncepcióknál látható, hogy a memória-sávszélesség növelése aránytalanul megnöveli a fogyasztást, vagyis egy új DRAM opció csak időhúzásra lett volna jó, de igazi megoldást nem jelentett volna az alapproblémára.

A lehetséges, de végül elvetett ösvények [+]

Végül az AMD egyik mérnöke 2008-ban előállt egy olyan ötlettel, amely elvi szinten pont ideális arra, amire szükség van. Ez a koncepció csupán annyi volt, hogy legyen a DRAM memória olyan közel a lapkához, amelyen közel csak lehet. Ennek akkor még nem volt neve, de gyorsan kiderült, hogy minden potenciális problémára megoldást kínál. Lehetővé teszi a rendkívül széles, több ezer bites memóriabuszok használatát, leegyszerűsíti a teljes memória-alrendszert, illetve a tokozásszintű integrációnak hála radikálisan nő az egységnyi fogyasztásra levetített memória-sávszélesség.

Az egyetlen komoly problémának az úgynevezett interposer réteg tűnt, amely összekötné magát a DRAM memóriát a lapkával. Ez azért volt komoly gond, mert ennek a rétegnek rendkívül vékonynak kellett lennie, miközben sok ezer vezeték elvezetésére volt szükség. A mérnöki kihívás tehát adott volt, és az AMD szövetkezett az ASE, Amkor és UMC trióval, hogy letegyék az interposerek tömeggyártásához szükséges technológiát. Messze ez volt a folyamat legnehezebb része, de az új évtizedben komoly eredményeket sikerült elérni.

A cikk még nem ért véget, kérlek, lapozz!