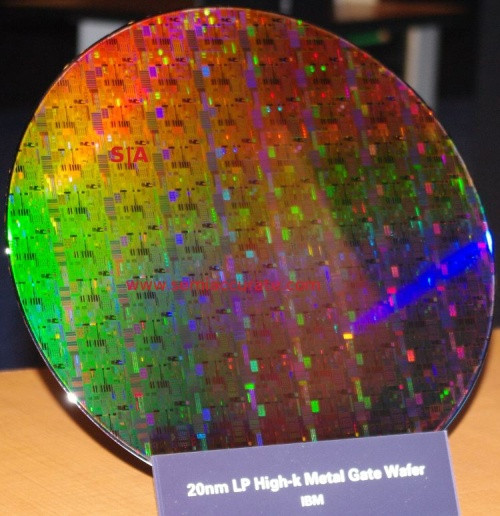

Az IBM a Common Platform rendezvényén bemutatott egy 20 nm-es LP gyártástechnológiával készülő wafert. A minta egy tesztchipet tartalmaz, ami valószínűleg számos eltérő áramkört használ, hogy megfelelő tapasztalatot gyűjtsenek a mérnökök az eljárásról. Az elmúlt héten már kiderült, hogy a Common Platform a 22 és 20 nm-es lépcső esetében a High-K dielektrikumú fém alapú kapuelektródákat alkalmaz gate last megvalósítással.

Hirdetés

A most bevezetendő 32 és 28 nm-es gyártástechnológiák a gate first eljárásra építenek, ám az új adatok szerint a váltás nem jelent majd semmilyen problémát. Ezt azzal magyarázták a cégek, hogy a gate first megvalósításon főleg a GlobalFoundries és a Samsung dolgozott, eközben az IBM a 22 és 20 nm-es gate last gyártástechnológia fejlesztésére koncentrált. A Common Platformon belül a három cég megosztja a technológiákat, ezzel elősegítve a gyors fejlesztési tempót, és az ezzel járó anyagi terhek kölcsönös felvállalását. Természetesen a 20 nm-es technológia még nincs bevethető állapotban, az IBM 2012-re tervezi a bevezetést.

Az IBM 20 nm-es waferje (forrás: SemiAccurate) [+]

A Common Platform beszélt a 20 nm-es eljárásnál alkalmazott technológiákról. Az áramkörök harmadik generációs immerziós litográfia használatával lesznek kialakítva, továbbá bevetésre kerül az SMO, azaz a Source Mask Optimization. A gyártás kialakításánál általános probléma, hogy az egyes minták kisebbek a rajzoláshoz használt fény hullámhosszánál, ami nem túl kedvező tényező. Az SMO ezen a problémán segít, megváltoztatva a fényforrást a precízebb eredmény érdekében. A 14 nm-es gyártástechnológia esetében bevezetésre kerül a negyedik generációs immerziós litográfia, továbbá ezen a csíkszélességen csak a SOI eljárás lesz alkalmazva, vagyis nem lesz bulk CMOS variáns. Ezt a konkurens gyártóknak is meg kell lépni, ugyanis 20 nm alatt elengedhetetlen valamely SOI struktúrát alkalmazása. Az ütemterv szerint a 14 nm 2014-re van tervezve, míg az ezt követő 11 nm-es technológia 2016-ban kerülhet bevezetésre.

Az IBM beszélt a 11 nm alatti 8, 5 és 3 nm-es csíkszélességekről is, ám ez egyelőre inkább elméleti, mint gyakorlati kérdés. A vállalatok elmondták, hogy PD-SOI-ról az FD-SOI struktúrára térnek majd át, és bevezetik a szilícium nanohúrokat. Természetesen erről kevés még az információ, hiszen számtalan problémát kell megoldani, így bármilyen előzetes terv felborulhat.