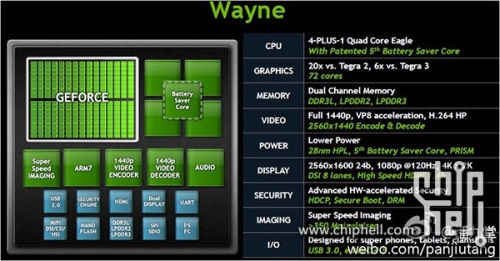

Nemrég írtunk arról, hogy az új generációs Tegra a CES-en mutatkozik be, de akkor még kevés információ állt rendelkezésre a Wayne kódnevű SoC felépítéséről. A ChipHell fórumán elérhetővé vált egy kiszivárgott dia, mely állítólag az új fejlesztés logikai vázlatát mutatja. Ez természetesen csak pletyka, de a paraméterek alapján valószínű, hogy helytálló információkat tartalmaz.

(forrás: ChipHell) [+]

A Wayne SoC a Tegra 3-nál alkalmazott felépítést használja a processzor oldaláról, vagyis a négy darab ARM Cortex-A15-ös processzormag mellett lesz egy ötödik kiegészítő erőforrás, mely terhelés nélkül, vagy alacsony igénybevétel mellett lesz aktív. Ekkor a többet fogyasztó főmagok lekapcsolhatók, ezzel az adott termék üzemideje megnövelhető. Az IGP oldalán már nagyobb változás lesz, így végre az NVIDIA is áttér a unified shader rendszerre, továbbá 72 darab shader processzor dolgozik majd a feladatok feldolgozásán. Az adatok szerint az új fejlesztés hatszor nagyobb teljesítményre lesz képes, mint amit a Tegra 3 IGP-je felmutatott. A memóriavezérlő támogatni fogja az LPDDR2, az LPDDR3 és a DDR3L szabványú lapkákat, de ennél is fontosabb, hogy kétcsatornás megoldásról lesz szó, vagyis az eddig alkalmazott 32 bites buszszélesség 64 bitesre nő.

A videók dekódolását és enkódolását fixfunkciós egység látja el, és az 1440p-s felbontású H.264-es és VP8-as formátumú anyagok is támogatva lesznek. Az új generációs Tegra a TSMC 28 nm-es HPL node-on készül, emellett értékes extra, hogy támogatja az USB 3.0-s interfészt is.