A TSMC frissítette gyártástechnológiákra vonatkozó útitervét, amelyből körvonalazódik a következő három év, ráadásul egészem ambiciózus projektekről beszélhetünk.

Hirdetés

Az idei esztendőt tekintve három node van sínen. Az adott kategórián belüli teljesítményű lapkákhoz érkezik az 5 nm-es N5A, ami az autóipart célozza, míg a 3 nm-es node szempontjából jön a N3E, ami valamivel kiforrottabb az eredeti N3-nál. Nagyon sokakat érdekelhet még az N4P, ami egy nagyon jó paraméterekkel rendelkező 4 nm-es eljárás, ráadásul relatíve olcsó is, így sok partner választhatja ezt az opciót a 3 nm-es irány helyett.

A 2025-ös tervek nagyrészt változatlanok, így a 3 nm-es opciók kiegészülnek még az N3P és az N3X verzióval, előbbi a teljesítménycentrikus kialakítás, míg utóbbi a HPC-piacra szánt lapkákat tartja szem előtt. A csúcsteljesítmény tekintetében a 2 nm-es node lesz a sztár, amellyel a TSMC FinFET-ről a saját GAAFET implementációjára vált. Ezen túlmenően a korábban tervezett N3AE (Auto Early) nem készül el, helyette alkalmazható lesz az előző bekezdésben említett N3E.

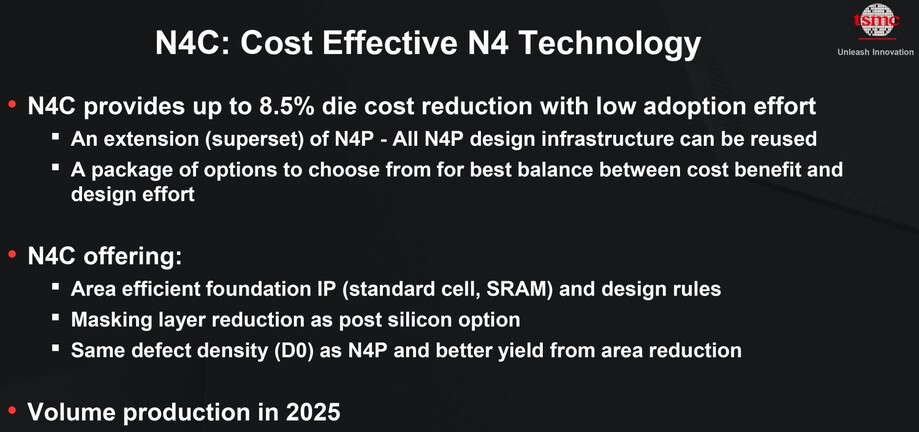

Várhatóan a 2025-ös év gyöngyszeme az N4C lesz, ami utolsó 4 nm-es mohikánként az N4P-t fejleszti tivább. Ez további költségcsökkentést fog eredményezni, és valószínűleg a TSMC itt arra számít, hogy nem kevés ügyfelük marad majd a bevált 5 nm-es osztályú eljárásokon, mert üzletstratégiailag kifizetődőbb, és jóval kisebb kockázatokat jelent.

A 2026-os esztendőben a 2 nm-es N2 kap N2P és N2X verziókat, szokás szerint ezek rendre teljesítménycentrikus és HPC-piacot célzó specializációk. Emellett érkezik az N3A, ami egy autóipari igényekre szabott 3 nm-es eljárás.

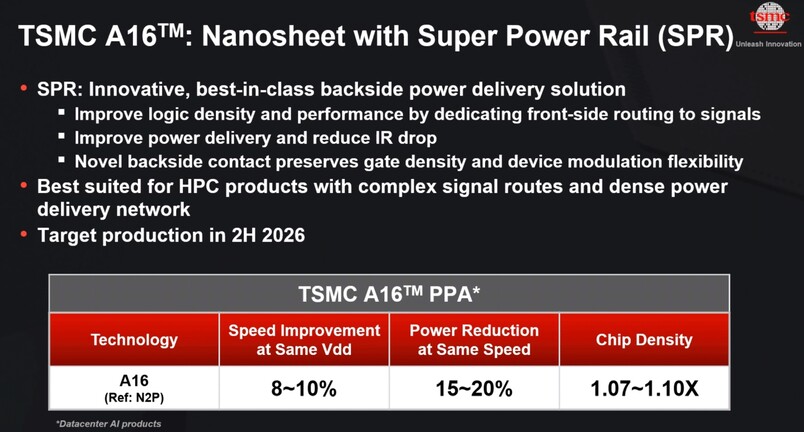

A 2027-es év még egy kicsit ködös, itt csak az A16-os, 1,6 nm-es eljárást vetíti előre a vállalat, ami az N2P-hez viszonyítva, egységes tranzisztorszám és órajel mellett 15-20%-os fogyasztáscsökkenést, illetve 8-10%-os teljesítménynövelést fog kínálni. Ez a node az ára miatt leginkább a HPC-piacot érdekelheti majd.