A MediaTek az idei évben komoly fejlesztésekkel szeretne előállni. Többek között már megírtuk, hogy a Helio X20 SoC rendkívül egyedi lesz, illetve az MT8163-as lapka sem lesz kevésbé érdekes, hiszen bemutatkozik benne a MediaTek Sapphire-lit kódnevű integrált grafikus vezérlője.

Hirdetés

A vállalat az újításokkal nem áll le, így most a CorePilot 2.0 került a középpontba. Az eredeti CorePilot nagyjából két éve mutatkozott be és a fő feladatának az számított, hogy az ARM Big.Little koncepcióval elérhetővé tegyék a heterogén többmagos dizájnt, amelynek keretében az operációs rendszer egyszerre látja az eltérő teljesítményű magokat, illetve azokat megfelelően is tudja kezelni. A CorePilot egyik fő előnye volt a konkurens eljárásokkal szemben, hogy viszonylag hatékonyan tudta belőni a processzormagok órajelét az adott feladatokhoz, így az adott hardver nagyrészt hatékonyan üzemelt. Erre vonatkozóan persze a konkurensek is kínáltak megoldásokat, így idővel mindenki elérte ezt a szintet.

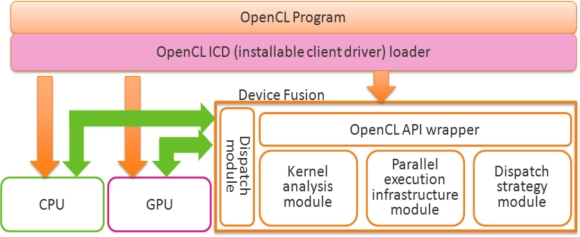

A MediaTek azonban most továbblép a CorePilot 2.0-val, amely az eredeti technika előnyeit kiegészíti a Device Fusion szolgáltatással. Az egész alapja egy virtuális OpenCL eszköz, ugyanis ennek a rendszernek a segítségével tudja úgy szétosztani a feladatokat egy CorePilot 2.0-t támogató SoC, hogy az egyszerre fusson a CPU magokon, illetve az IGP-n is.

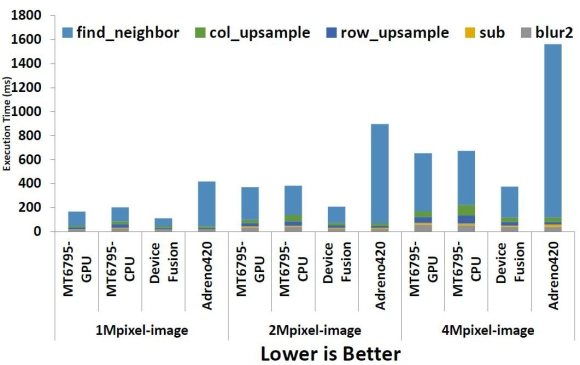

A MediaTek a CorePilot 2.0-t támogató MediaTek MT6795-ös lapkával kimérte a Device Fusion szolgáltatás előnyeit az MT6795 CPU-s és IGP-s eredményeihez, valamint a Qualcomm Snapdragon 805-höz viszonyítva.

A tesztelt képfeldolgozási algoritmus számításigénye meglehetősen nagy, és öt fázisra volt osztva a feldolgozás. Látható, hogy mindhárom tesztben az érkező, CorePilot 2.0-t támogató SoC volt a leggyorsabb, nem is kevéssel. A MediaTek szerint ennek az az oka, hogy a CorePilot 2.0-val az adott fázis azon a részegységen fut, amelyen a leghatékonyabb.

A korábbi gyorsítási koncepciókkal az a legnagyobb probléma, hogy a lapka processzorrésze nagyon jó bizonyos feladatokban, de van olyan számítás, ahol már nem hatékony. Ugyanez igaz az integrált grafikus vezérlőre is. Azzal, hogy a feldolgozás fázisait rákényszerítjük az egyik részegységre csak azt érjük el, hogy bizonyos fázisok begyorsulnak, míg a többi lelassul. Ez nagyon jól látható az MT6795-ös lapkán, ahol a processzorrész és az IGP nagyjából hasonló teljesítményre volt képes.

A MediaTek algoritmusára lebontva az elemzést látható, hogy a find_neighbor fázis nagyon lassú a grafikus vezérlőkön, míg a többi fázis a processzorrészen szenved. A CorePilot 2.0 innentől kezdve egyszerűen kezeli a dolgot, mivel a find_neighbor fázist a processzorrészen, míg a többit az integrált grafikus vezérlőn futtatja.

Más feladat esetében is hasonlóan előnyös a rendszer. Például az arcdetektálás során az egyes fázisok más részegységeken futnak le, ami a tiszta CPU-s számításhoz képest 22%-kal, míg az IGP-s opcióhoz képest 146%-kal gyorsabb feldolgozást kínál, miközben rendre 17%-kal és 18%-kal csökken a lapka energiaigénye. A MediaTek szerint utóbbi az, ami rendkívül vonzóvá teszi a heterogén programozást az ultramobil piacon, mivel úgy lehet elérni gyorsulást, hogy közben üzemidőt spórolható meg.