- AMD K6-III, és minden ami RETRO - Oldschool tuning

- A Gigabyte is visszaveszi alaplapjainak alapértelmezett tuningját

- Házimozi belépő szinten

- Milyen SSD-t vegyek?

- Autós kamerák

- Házimozi haladó szinten

- Hobby elektronika

- AMD Ryzen 9 / 7 / 5 7***(X) "Zen 4" (AM5)

- Milyen billentyűzetet vegyek?

- Faragott a Radeon RX 7700 XT árán az AMD

Hirdetés

-

VR játék lesz az Alien: Rogue Incursion

gp Az év végén érkező program PC-re, Meta Quest 3-ra és PlayStation VR2-re érkezik a tervek szerint.

-

Igencsak szerény méretekkel rendelkezik az Aetina Xe HPG architektúrás VGA-ja

ph Az 50 wattos modellt beágyazott rendszerekbe, MI-vel kapcsolatos munkafolyamatokhoz és edge applikációkhoz szánták.

-

Olcsó 5G-s ajánlatot nyújt a Realme Indiának

ma Megérkezett a Realme C65 5G, az első készülék a MediaTek Dimensity 6300-zal.

Új hozzászólás Aktív témák

-

Oliverda

félisten

válasz

Balala2007

#24

üzenetére

Balala2007

#24

üzenetére

Köszi, az első javítva!

A másodikra:

Régóta tudják a processzorok, hogy az XOR reg,reg vagy SUB reg,reg azonos regiszterre nem függ a regiszter előző értékétől, viszont a Sandy Bridge az első, ahol a regiszter file nullázza a regisztert, így nem kell hozzá végrehajtó egység.

Intel Opt. Manual, Sandy Bridge:

"2.3.3.1 Renamer

Instruction paralellism can be improved by using common instructions to clear register contents to zero. The renamer can detect the on the zero evaluation of the destination register.

[...]Since zero idioms are detected and removed by the renamer, they have no execution latency."Pl. ezen a képen a Zeroing Idioms néven látható

Real World Tech, Sandy Bridge:

"Another small benefit of a PRF-style design is zeroing registers. A common idiom in x86 code is clearing a register by XORing it with itself, to break any dependencies. In previous generations, this required a uop in one of the ALUs to overwrite the register. However, with a PRF-based design, zeroing a register can be accomplished solely within the renamer – by simply adding the register to the list of freely available registers in the PRF." [link]

"Instructions that need no execution unit

The abovementioned special cases where registers are set to zero by instructions such as XOR EAX,EAX are handled at the register rename/allocate stage without using any execution unit. This makes the use of these zeroing instructions extremely efficient, with a throughput of four zeroing instructions per clock cycle."

"Minden negyedik-ötödik magyar funkcionális analfabéta – derült ki a nemzetközi felmérésekből."

-

Balala2007

tag

válasz

Balala2007

#151

üzenetére

Balala2007

#151

üzenetére

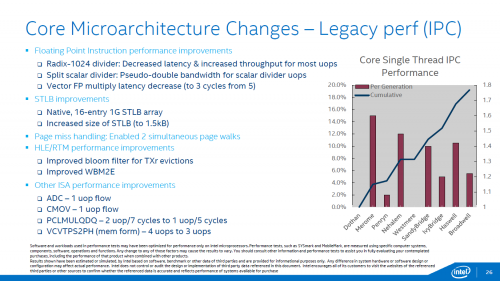

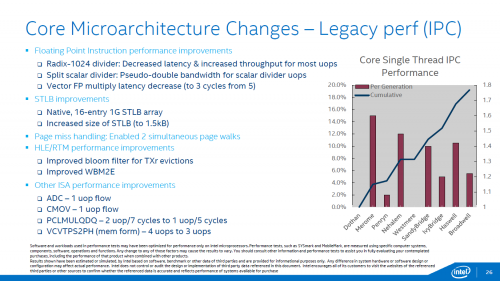

Erdekesseg, igy gondolkodik az Intel az IPC novekedesrol:

A XeonD bemutato pdf-bol van, ezert nincs meg rajta a Skylake.[ Szerkesztve ]

AIDA64.com

Új hozzászólás Aktív témák

ph Utánajártunk, hogy az elmúlt 7 évben miként változtak, mennyit gyorsultak az Intel egyes mikroarchitektúrái.