További fejlesztések

A Hyper-Threading egy olyan funkció, amire egyesek szívesen emlékeznek vissza, míg mások nem rajonganak érte; a Pentium 4-et jónéhány esetben lelassította. Amit meg kell érteni, az az, hogy a Core architektúra (azaz a Nehalem) jóval szélesebb back-end résszel rendelkezik, több a végrehajtó egység, több a potenciálisan kihasználatlanul álló erőforrás, tehát a HTT – ellentétben a Pentium 4-es tapasztalatokkal – ténylegesen javíthat a Core (Nehalem) processzorok teljesítményén. Először is a Hyper-Threading technológia megjelenésének hatására be kellett következnie pár változásnak. A Hyper-Threading miatt duplikálták a regiszterfájlokat, az RSB-t és a Large-page iTLB-t. Felparticionálták, azaz a szálak között statikusan felosztották a Load és Store puffereket, a ROB-ot és a Small-page iTLB-t. Az egyik legérdekesebb a Nehalemben, hogy vannak olyan részegységek, amelyekért az egyes programszálaknak versengenie kell, ezek a Reservation Station, a gyorsítótárak, az adat TLB és a másodszintű TLB. A futószalagon egyedül a végrehajtóegységeket képtelenség megosztani, azok egyszerűen csak végzik a dolgukat, ami jön, azt végrehajtják. Ha belegondolunk, akkor a ROB statikus felosztása révén az a 128 bejegyzés tárolására képes kis puffer nem is olyan egetverően nagy, hiszen két szálnak kell rajta osztoznia, tehát egy-egy szál 64 darab bejegyzést birtokolhat egyszerre. Annyit sikerült még megtudnunk, hogy amikor csak egy szálon folyik a munka, olyankor az az egyetlen szál használhatja a teljes ROB-ot. A dinamikusan felosztott Reservation Station 36 egységnyi szélessége sem éppen kiemelkedő, de éppen ezért dinamikus a megosztás: az RS-t az a szál használhatja, amelyik a program viselkedése alapján a legjobb eredménnyel, leggyorsabb végrehajtási idővel kecsegtet.

A cache-hierarchia is jelentős átalakuláson ment keresztül. Az elsőszintű gyorsítótárhoz csak kis mértékben nyúltak hozzá, a Nehalemben a Core 2-höz hasonlóan 32-32 kB adat és utasításcache található, melyek 8 és 4 utas csoportasszociatív tárak, és bár ezek kicsit lassabbak a Core 2-ben találhatónál (3 helyett 4 ciklusnyi az elérési idő), több cache-blokk olvasási hibát engedélyeznek. Ellenben a Nehalem másodszintű gyorsítótárának mérete a töredéke a Core 2-ben találhatónak, mindössze 256 kB, és szintén 8 utas csoportasszociatív. A kis mérethez nagy sebesség társul, az L2 cache-nek csökkent a késleltetési ideje. A harmadszintű gyorsítótár megjelenése újdonság: 8 MB méretű, 16 utas csoportasszociatív, megosztott a processzormagok között és inkluzív, azaz az összes L1 és L2 gyorsítótárban megtalálható információt tárolja: az Intel szerint ez sokkal jobb megoldás, mint az AMD által alkalmazott exkluzív cache, mert így az adatkeresgéléshez szükséges forgalom csökkenthető, bár azt nem teszik hozzá, hogy így a kihasználható terület viszont kisebb. Az L3 cache-ben való keresgélést cache-cellánként négy "core valid" bit segíti, melyek megmutatják, hogy a keresett információ megtalálható-e valamelyik gyorsítótárban vagy sem.

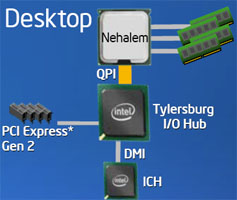

Már eddig is rengeteg újdonságról esett szó, de van még valami, ami gyakorlatilag már önmagában is kiemelkedő jelentőségű. Az Intel évtizedek után úgy döntött, hogy végleg megválik a rendszerbusztól. A Nehalem az első olyan Intel processzor, amely pont-pont összeköttetésen keresztül kommunikál a rendszer többi elemével, ez pedig a QuickPath Interconnect (QPI). Ez a megvalósítás ismerősen hangzik, hiszen az AMD már a K8-tól kezdve egy ehhez hasonló linket használ (HyperTransport), de úgy tűnik, hogy az Intel nem kért ebből, hanem inkább egy saját szabványt fejlesztett ki. A QPI A HT-linkhez hasonlóan egy csomag alapú, magas sávszélességet és alacsony késleltetést kínáló protokoll, mely full-duplex (kétirányú), maximálisan 25,6 GB/s-os adatáteresztő képességgel rendelkezik. A QPI megjelenése a mobil, illetve asztali processzorok szempontjából kevésbé lényeges kérdés, a szerverek piacán viszont annál fontosabb, hiszen a rendszerbusz megléte volt az Intel processzorok köré épülő szerverek skálázódásának egyik legnagyobb problémája, és ez most a QPI bevezetésével kiiktatásra került.

Egy szintén jelentőségteljes újítás az integrált DDR3-as memóriavezérlő (IMC, Integrated Memory Controller) bevetése. Az AMD által még a K8-asnál bemutatott specialitást az Intel megfejelte egy harmadik csatornával, ami így 1066-os memóriákkal maximálisan 32 GB/s-os sávszélességet kínál, egyben jelentősen lecsökkentve a memóriaelérés idejét is. Az FB-DIMM támogatás valószínűleg csak a szerverváltozatok sajátja lesz (Beckton vagy Nehalem EX), egyelőre be kell érni a DIMM, UDIMM és RDIMM modulokkal.

A QPI és az integrált memóriavezérlő oda-vissza kölcsönhatásban áll a processzor egyes elemeivel. Például az Intelnek többé nincs szüksége batárnagy gyorsítótárakra csak azért, hogy kiküszöbölje a rendszerbusz lassúságát, azt a sokmillió tranzisztort ehelyett felhasználhatja valami okosabb dologra is. A háromlépcsős gyorstár (a Nehalem L3-asa közel a processzor órajelén fut, a K10-eséhez képest alacsony a késleltetése) és az IMC rendkívül gyors hozzáférést ad az adatokhoz, amire az SMT miatt, főleg szerverkörnyezetben szükség is van. Összességében az látszik, hogy az Intel nem bízott semmit a véletlenre.

Végül, de nem utolsósorban a Nehalemben debütál az SSE4.2 SIMD-utasításkészlet, ami hét új utasítást tartalmaz: egy részük az XML, illetve szöveg, azaz stringfeldolgozásra specializálódott, továbbá tartalmaz speciális területekre fókuszáló, különböző mintafelismerő instrukciókat is (pl. kézírás felismerés [ATA], génkutatás [Popcnt] stb.). A CRC32-es utasítás a háttértárolók és hálózati adatfeldolgozás felgyorsítására szolgálnak. Egyelőre nincs túl sok program, ami kihasználná ezeket, de az SSE-utasításkészletek közül eddig egy sem merült feledésbe, és mindig csak a megjelenésüket követően kerültek kihasználásra.

Miután már ismerjük a Nehalem futószalagját, van még valami, ami igazán érdekessé teszi az egész architektúrát: ez pedig a moduláris felépítés. Az Intel egy olyan rendszerarchitektúra megalkotásán fáradozott, mely a piac összes szegmensében képes helytállni, mindezt úgy, hogy ne kelljen különböző további fejlesztésekkel, járulékos költségekkel terhelni a céget. A processzortervezésnek ez az új módozata, ami korántsem az Intel találmánya, egy, már szélesebb körben alkalmazott paradigma. A Nehalem az Intel első olyan fejlesztése, melynek értelmében a processzor egyes funkcionális elemeit, ez esetben a magokat, a gyorsítótárakat, a QPI linkeket, a memóriavezérlőt, energiamenedzsmentet stb. külön-külön fejleszthetik; jól definiált interfészek és a gyártáselőkészítéssel összehangolt tervezési rendszerek teszik lehetővé, hogy ezen elemekből többféle igényt kielégítő processzorok születhessenek. Gondoljunk csak az előző generációra, a notebookon át a szerverekig egyazon architektúra hajtotta meg a különböző rendszereket, pl. a Meromot találjuk meg a notebookokban, ennek asztali változata a Conroe, a szerverekbe pedig a Woodcrest került: néhány kisebb differenciát leszámítva ezek egyetlen fejlesztésen alapultak.

A Nehalem az Intelnek lehetőséget ad arra, hogy tetszőlegesen összekombinált processzorokat készítsen, pl. a notebookba felesleges az L3 cache, nincs szükség integrált memóriavezérlőre, a QPI-linkek száma is alacsonyabb, viszont jól jöhet egy integrált videovezérlő, ennek megfelelően alakítható ki egy-egy termékszegmens. A Nehalem négymagosként mutatkozik be, de később megjelennek majd a két- (belépőszintű asztali rendszerek) és nyolcmagos, (azaz 16 párhuzamos utasításszál végrehajtására alkalmas) szerverekbe szánt változatok is. A processzor ilyen irányú felépítése természetesen magában hordozza a chipsetek jelentőségének csökkenését is, az egyforma magok és különféle chipsetek párosításait a standard chipsetek és eltérő magok fogják felváltani.

Az új architektúrát az energiamenedzsment terén is továbbfejlesztették, megjelenik a processzorban a Power Control Unit, azaz PCU, egy mikrokontroller, egy miniprocesszor a processzoron belül, ami a központi egység egyes részegységeinek az áramellátásáért és monitorozásáért felelős. Ez az adott szituációnak megfelelően külön-külön szabályozza a magok, az északi híd és a harmadszintű gyorsítótár hőmérsékletét és fogyasztását. A PCU alapjában véve az AMD K10-es energiamenedzsmentjéhez hasonlóan működik, tehát a processzormagok járhatnak egymástól eltérő órajelen, de a feszültség mindig a legjobban leterhelt processzoréhoz igazodik. Viszont van különbség is, méghozzá az, hogy a PCU képes az egyes processzormagokat alvó állapotba (C6 state) küldeni, vagyis teljesen átamtalanítani azokat, amikor nincs rájuk szükség, ezzel elfojtva még a szivárgási áramból fakadó fogyasztást is. A Nehalemben található PCU az energiamenedzsment terén sokkal gyorsabban dolgozik, mint elődei, ami azt jelenti, hogy a processzor egyes részegységeinek állapotváltása közti időkiesés (latency) is alacsonyabb.

Az új processzorok egyik legszembeötlőbb funkciója a Turbo mód, amit szintén a PCU tesz lehetővé. A Turbo mód nem újdonság, hiszen a mobil Penryn lapkák már ismerték ezt a funkciót Enhanced Dynamic Acceleration Technology néven, de a gyakorlatban szinte sehol sem működött a szoftveres támogatás hiánya miatt. A Nehalem Turbo módja azonban más, mert a PCU egy hardver, nincs szüksége külső segítségre. A funkció bekapcsolását követően a PCU figyelemmel kíséri a processzor kihasználtságát, majd amint a futtatott folyamatoknak nincs szüksége a processzor összes erőforrására, a nem használt magokat lekapcsolja. Ennek megfelelően a fogyasztás csökken, azonban a Turbo módot aktiválva az éppen leterhelt magok órajelét a rendszer dinamikusan megemeli, amíg a processzor el nem éri a specifikációkban megadott tipikus hőtermelési (TDP) értékét. A Turbo mód akár négy aktív processzormag esetében is megemelheti az órajelet, amíg a PCU úgy érzékeli, hogy a hőmérsékletek rendben vannak és az aktuális fogyasztás a maximált érték alatt van. Alapértelmezett beállítások mellett természetesen nem kell drasztikus teljesítménynövekedésre számítani.

A cikk még nem ért véget, kérlek, lapozz!