Mi van a Broadwellen belül?

A Broadwell esetében az Intel által megadott adatok alapján vizsgálható a processzor és az integrált grafikus vezérlő architektúrája, de ezt a vállalat csak a Core M-hez használt lapkára szűkítette. Persze ez nem jelent túl nagy gondot, hiszen a nagyobb lapkák duplaannyi processzormagot, utolsó szintű gyorsítótárat, illetve IGP multiprocesszort kaphatnak, tehát annak ellenére, hogy az Intel ezekről nem beszélt, a skálázás módja így is nyitott könyv.

Hirdetés

A processzormagok, illetve a megosztott gyorsítótár szempontjából nincs eget rengető változás a Haswellben használt opcióhoz képest. Komolyabb változásként említhető, hogy az utasítások sorrendtől független végrehajtásáért felelős out of order logika nagyobb ütemezőt kapott, gyorsabb lett a lebegőpontos szorzás, a Radix osztómotor, illetve számos kriptográfiai utasítás, valamint a virtualizáció. Összességében ez azt jelenti, hogy bizonyos esetekben a Haswellhez képest 5%-kal nő az IPC, vagyis az egy órajelciklus alatt elvégzett műveletek száma. Azonos órajelet feltételezve a legtöbb esetben nem érdemes lényegi változásra számítani a Haswellhez képest.

Az integrált grafikus vezérlő már sokkal nagyobb módosításokon ment keresztül. Egyrészt bemutatkozik a Gen8 architektúra, amely az elődhöz hasonlóan 4 kB-os lapokkal dolgozik, de a benne elhelyezett gyorsítótárak sorainak mérete 64 bájt. Bár az említett adatokat nem szokás kiemelni, de pont erre a változásra van szükség ahhoz, hogy a Broadwell támogassa az egységes memóriát. Nem nehéz kitalálni, hogy az x86/AM64 architektúrára alapozó processzormagok is az előbb említett paraméterekkel dolgoznak. A másik lényeges újdonság, hogy az IGP kapott egy MMU-t (memóriamenedzsment egység), aminek majd a DirectX 12-ben lesz igazán komoly haszna, ahogy azt egy korábbi cikkünkben már ecseteltük.

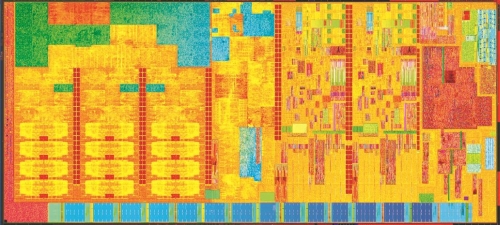

A Core M-hez használt Broadwell lapka

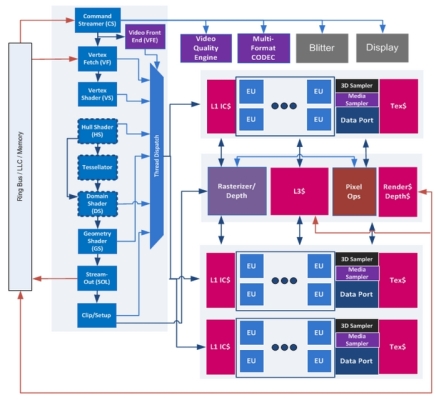

A grafikus számítások szempontjából a Gen8 architektúra – elődeihez hasonlóan – továbbra is három jól elkülöníthető részre osztható. A setup motor a Haswell IGP-jéhez képest nem változott, míg a kalkulációkért a már megszokott a shader tömb felelős, amelyből az új dizájn mellett maximum hat darab kaphat helyet; tulajdonképpen ez az egység a hagyományos értelemben vett multiprocesszor. Ebben mostantól maximum 8 darab Execution Unit lesz fellelhető. Ezek továbbra is komplex feldolgozók, így megmarad bennük a két darab 128 bites vektormotor. Utóbbiak közül az egyik felel az általános operációk feldolgozásáért, míg a másik a speciális, trigonometrikus és transzcendens utasításokat támogatja, de mindkét vektoros egység kezeli az FMA-t, ami rögtön utat ad a 4+4 co-issue képességnek. Ezzel tehát az Execution Unitok továbbra is órajelenként nyolc darab, egymástól független FMA utasítást képesek végrehajtani. Természetesen a függőség kezelése kulcsfontosságú maradt, mivel az egymástól függő operációk párhuzamos feldolgozása nem lehetséges. Erről ezúttal is a Thread Dispatch egység gondoskodik, amely igyekszik úgy etetni a vektormotorokat, hogy minél többször hasznosítható legyen a 4+4 co-issue feldolgozás. Mindemellett az alaparchitektúrát érintő finomítás, hogy javult a 32 bites integer műveletek feldolgozási sebessége.

A 8 darab Execution Unit egy shader tömbön belül visszalépésnek tűnhet, valójában viszont pont, hogy előrelépés történt. Az Intel a Sandy Bridge megjelenése óta komoly utat járt be az IGP fejlesztése szempontjából. A shader tömbben található feldolgozók száma gyakorlatilag minden generációban változott, ami egyetlen más, GPU-architektúrát tervező cégre sem jellemző. Maga a folyamatos módosítás azt jelzi, hogy a mérnökök egyszerűen nem találják az optimális konfigurációt. Az Ivy Bridge Gen7-es IGP-je esetében egy shader tömb 16 feldolgozót használt, és ez a szám a Haswell Gen7.5-ös megoldásánál 10-re csökkent, majd ahogy említettük, mostmár csak 8 darab Execution Unitról beszélhetünk. Ez tulajdonképpen azt jelenti, hogy a fejlesztés visszatért ahhoz a kiindulási ponthoz, ahol az Intel az egész HD Graphics vonalat elkezdte. Egyetlen dolog változott: az Intel mérnökei tapasztaltabbak lettek, így rájöttek, hogy rossz irány a shader tömbön belüli feldolgozókat növelni.

A Gen8 architektúra új irányt vett a hatékonyság és a jobb skálázhatóság elérése érdekében: a feldolgozók helyett az L1 gyorsítótár mérete nagyot nőtt a shader tömbökön belül. Ebben van is logika, mivel az eddigi adatok szerint az Intel problémája arra vezethető vissza, hogy hiába van sok feldolgozó a rendszerben, azok etetésére nem tartható fent elég sok szál az IGP-n belül. Ez a többi GPU-architektúrával összehasonlítva is eléggé szembeötlő, hiszen amíg az Intel egy teljes IGP-re nem használ ötszáz szálnál többet, addig a konkurens AMD és NVIDIA architektúrái csupán egyetlen multiprocesszoron is ezer vagy akár több szálat futtatnak. Mivel a futtatható szálak száma eléggé kötött paraméter az efféle architektúráknál, így ennek drasztikus emelésével nem érdemes próbálkozni, hiszen az felborítaná a jól megtervezett szinkronizációt a szálak között.

Az L1 gyorsítótár mérete azonban növelhető, és ez azt eredményezi, hogy az egy Execution Uniton belül futtatható maximális hét szál közül van esély rá, hogy egy vagy két szál számára ott lesz a szükséges adat az L1 gyorsítótárban, amivel a rendszer dolgozhat addig, amíg a többi szál számára is befut a szükséges információ. A gyorsítótár növelésének biztos lesz eredménye hatékonyság tekintetében, viszont érezhető hátrány, hogy jóval méretesebb lett az IGP, mint bármikor korábban. A Core M termékekhez alkalmazott lapkán az IGP akkora területet foglal el, amelyre négy darab extra Broadwell mag is építhető a hozzájuk tartozó gyorsítótárakkal együtt. Ráadásul ez még nem is a legnagyobb IGP konfiguráció, hiszen lesz egy duplaekkora opció is, amelynek helyére nyolc darab extra Broadwell mag férne el. Persze ezek inkább elméleti adatok, de látható, hogy a gyorsítótárak méretének növelése drasztikus hatással van az IGP helyigényére, ami arra is magyarázatot ad, hogy az Intel miért próbálkozott korábban inkább a feldolgozók számának növelésével.

A Core M-hez használt Broadwell lapka IGP-je [+]

A shader tömbökben szokás szerint megmarad a 256 kB-os kapacitást kínáló URB, azaz a Unified Return Buffer, mely egy gyorsan elérhető, írható és olvasható megosztott memória az Execution Unitok között. A textúrázás szempontjából sok változás nincs, azaz egy shader tömb két darab megosztott textúrázó blokkot tartalmaz, melyek egyenként négy darab Gather4-kompatibilis textúrázó csatornát alkalmaznak. Természetesen jelen van a blokkonkénti textúrázó gyorsítótár is, mely egy 4 kB-os elsődleges és egy 24 kB-os másodlagos szintből áll. A shader tömbök mellett található a render tömb, mely a data porton keresztül érhető el. Utóbbi tartalmazza a ROP-blokkot is, melyben négy blending és négy Z mintavételező egység dolgozik. Ezen a ponton tehát nincs változás a korábbi IGP-khez képest, viszont nőtt a ROP blokkhoz tartozó gyorsítótárak mérete. Megmaradt az L3 gyorsítótár is, ami az IGP saját, szabadon felhasználható memóriája, és ide a processzormagok nem írhatnak semmit. Ráadásul ennek mérete 256 kB-ról 384 kB-ra nőtt. Ezzel kapcsolatban fontos még megjegyezni, hogy az L3 gyorsítótér felel a Local Data Share (LDS) funkció ellátásáért is.

Konfigurálás szempontjából az Intel kétféle dizájnt kínál majd. A Core M termékekhez készült lapkában három shader tömb és egy render tömb lesz, ami összesen 24 darab Execution Unitot eredményez. A nagyobbik dizájn már hat shader tömbot és két render tömböt alkalmaz, vagyis a setup motoron kívül minden meg lesz duplázva az IGP-n belül. Kiemelendő még, hogy a Broadwell Gen8-as architektúrája már nem csak a négyszeres, hanem a kétszeres mintavételi módot is támogatja az MSAA aktiválásakor, ami azt jelenti, hogy a kétmintás (2x) opcióért már nem kell a négymintás (4x) MSAA sebességével fizetni. Ezt az Intel különálló blokkokkal oldja meg, vagyis a mérnökök beépítettek egy hardveres részegységet a kétmintás és egyet a négymintás MSAA-nak is. Ez technikailag tranzisztorpazarlás, de a végeredmény tekintetében abszolút működőképes megoldás. Mint ismeretes, a Haswell IGP-je ebből a szempontból furán működött. Mindemellett egy harmadik blokk képes a nyolcmintás MSAA-ra is.

A cikk még nem ért véget, kérlek, lapozz!