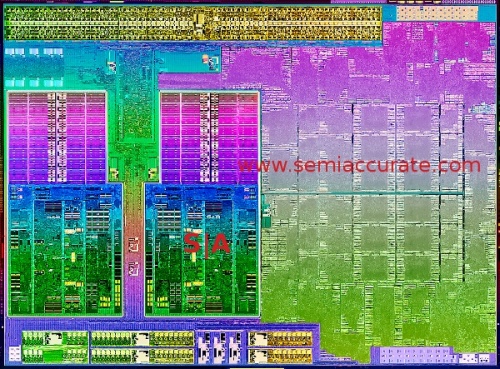

Az AMD az év első felében mutatja be a Trinity APU-t, mely a Fusion termékskála második generációjának tekinthető, így elsősorban az optimalizálás lesz a főszerep. A Semiaccurate hozzájutott egy fotóhoz, mely a lapka fizikai felépítését mutatja, amiről sok információ leolvasható. Elsőként a lapka láthatóan meghízott, illetve inkább hosszabb lett. Számításaink szerint a kiterjedése 250 mm² körül lesz, így hozzávetőleg 10%-kal nagyobb a Llano APU-nál.

Összegezve az eddig ismert részleteket: a Trinity a Llano APU-hoz hasonlóan 32 nm-es SHP gyártástechnológiával készül, és a processzormagok, illetve pontosabban modulok a Piledriver kódnévre hallgatnak. Ezek az egységek az aktuális Bulldozer modul továbbfejlesztései, többek között jobb energiamenedzsmentet, Turbo Core 3.0-t, új utasításkészleteket és valamivel nagyobb teljesítményt kínálnak. A lapkában két modul lesz, amit az AMD négy magnak tekint. A modulok egy-egy 2 MB-os másodszintű gyorsítótárat kapnak, miközben az L3 gyorsítótár lemarad. A kétcsatornás memóriavezérlő hivatalosan is támogatja majd a 2133 MHz-es órajelen üzemelő DDR3 memóriákat, a JEDEC szabvány szerinti 1,25, 1,35 és 1,5 voltos üzemfeszültségek mellett. Szokás szerint lehet gyorsabb memóriát is használni, de az tuningnak számít majd.

AMD Trinity APU (forrás: Semiaccurate) [+]

A chip grafikus vezérlőjével kapcsolatban már jóval kevesebb adat állt eddig rendelkezésre. Korábban arról szóltak a pletykák, hogy a szuperskalár shader processzorok az úgynevezett VLIW4 struktúrát használják. Ezt a kiszivárgott fotó, ugyan nem cáfolja, de látható, hogy a lapkában hat darab shader tömb található, így sokkal valószínűbb, hogy marad a VLIW5 struktúra. Ez a Dual Graphics szempontjából is logikus opció, hiszen az olcsóbb termékek az előző generációból kerülnek ki. A hat darab tömb VLIW5 struktúrával számolva 480 shader processzort jelent, amihez 700 MHz körüli magórajel társulhat majd. Természetesen elképzelhető a VLIW4 struktúra is, de ebben az esetben az AMD által előzetesen felvázolt elméleti számítási kapacitáshoz 1 GHz-es magórajel kellene, ami viszonylag magas feszültség mellett hozható, persze mindez távolról sem lehetetlen.

Az AMD asztali piacra szánt Virgo platformjáról korábban már kiderült, hogy az UVD motor megmarad a 3.0-s verziónál, de kiegészül a SAMU-val, ami a Secure Asset Management Unit rövidítése. Ez a rendszer tehermentesíti a CPU-magokat a védett tartalmak titkosításának feloldása alól, így például Blu-ray filmek lejátszása mellett jelentősen csökkenhet a fogyasztás. Szintén extra képesség a VCE, vagyis a Video Codec Engine, ami lényegében a Tahiti cGPU esetében részletezett hardveres enkódoló motor. Régebben már megerősítést nyert a hárommonitoros Eyefinity támogatása is, valamint a DisplayPort 1.2-es port is alkalmazható a Virgo platform esetében. A PCI Express vezérlő képességeiről nehéz következtetéseket levonni a kép alapján, de jól látható módosításokkal élt az AMD, így elképzelhető a 3.0-s PCI Express felület támogatása.

A szoftveres szempontok alapján az AMD a Fusion termékskála hagyományait követi, vagyis a megjelenéskor elérhető összes gyártófüggetlen felület és API támogatása biztosított.

Információink szerint a Socket FM2-es tokozású Trinity APU-k az A jelzésű széria részei lesznek, azon belül is A4-es, A6-os, A8-as és A10-es verziók várhatók 5000-es számozással. Az asztali piacon 65, 100 és 125 wattos TDP keretek lesznek, míg a mobil termékek esetében 17, 35, illetve 45 wattos értékekre van kilátás.