TLC, a régi-új NAND

Az utóbbi bő egy év során drasztikus áresést tapasztalhattunk az asztali SSD-k piacán, ami több okra vezethető vissza. A NAND-alapú meghajtók tervezése és gyártása jóval egyszerűbb, mint a merevlemezeké. A két kötelező fő komponens (vezérlő és NAND chipek) viszonylag könnyen beszerezhető valamelyik nagy gyártótól; megfelelő tervezői szakértelemmel és rutinnal párosítva őket már szinte kész is a szupergyors meghajtó. Ezen nagy egyszerűség okán meglehetősen sok cég nézte ki magának a piac szép profittal kecsegtető SSD tortáját. A nevezők között nagy számban találhatunk különféle, korábban szinte kizárólag DRAM-alapú termékekkel foglalkozó vállalatokat, ami nem is csoda, hisz az SSD utóbbi részegységekkel igen közeli rokonságot ápol.

Másfél év alatt bő 60%-os áresés [+]

A piaci szereplők elszaporodása mellett az egyes komponensek gyártási költségei is folyamatosan normalizálódtak. A merőben új alapokra helyezett termékek esetében különösen jellemző, hogy a sorozatgyártás felfutásával fordítottan arányosan csökken az előállítási költség, ami jó esetben az árcédulákon is visszaköszön. Itt említhetnénk példaként a manapság már széles körben elterjedt TFT monitorokat, melyek jó néhány évvel ezelőtt szinte csillagászati árral debütáltak. A kezdeti nehézségekre aktuális példa lehet az OLED, amely technológia továbbra is a szárnybontogatás fázisában mozog, ehhez mérten méregdrága kereskedelmi áron.

Azonos kapacitás kisebb területen

Most kanyarodjunk vissza az SSD-k világához, és ott is az egyik fő komponenshez, a NAND lapkához. A processzorok világában otthonosan mozgó olvasóink valószínűleg jól tudják, hogy ugyanazon dizájn helyigénye teljes csíkszélesség-váltás esetében pontosan feleakkora területre redukálható, ergo ezzel a lépéssel egyetlen szilíciumostyára közel kétszer annyi lapka férhet fel. Természetesen az adott gyártástechnológia kifejlesztése és felfuttatása igencsak erőforrás-igényes folyamat, aminek teljes megtérülése időbe telik. Előbbi megállapítás alól a NAND lapkák sem képeznek kivételt, azaz egy teljes ugrással – egységnyi területet tekintve – a cellák számával egyenesen arányosan megduplázható a tárkapacitás.

Ez elsőre még jól hangzik, de sajnos a csíkszélesség csökkenésével nő a vezérlő részéről szükséges hibajavítások (ECC) száma. Ez egy nagyobb számítási kapacitással bíró, "okosabb" kontroller számára nem lehet különösebb probléma. (Minden bizonnyal ezért is zsúfolnak bele egyre több magot az SSD-k vezérlőjébe.) A másik probléma a cellák élettartama, ami sok esetben a csíkszélességgel együtt csökken. Erre a jelenlegi NAND-technológián belül egyelőre nincs tökéletes megoldás. Természetesen a gyártók sokat dolgoznak azon, hogy az egyre intelligensebb vezérlésnek köszönhetően óvják a lapkákat a felesleges írási műveletektől. A már jól ismert SandForce erre egy tömörítési eljárást is kidolgozott, aminek köszönhetően az arra alkalmas adatok kevesebb művelettel (írási ciklussal) tárolhatók el, és ez a chipek élettartamára (is) jó hatással van.

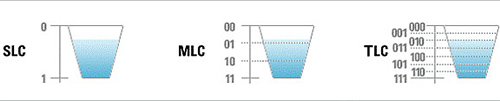

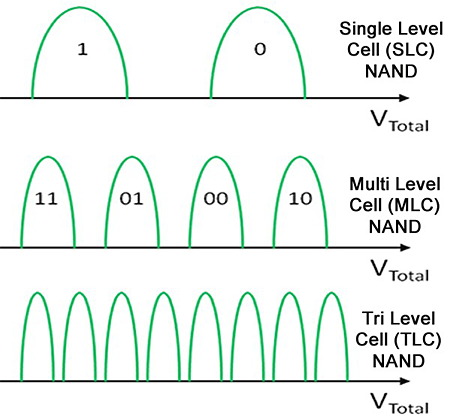

Az SSD-k fejlődését a kezdetektől nyomon követő olvasóink biztos jól emlékeznek még az első, SLC (single-level cell) alapú meghajtókra, amiket nem sokkal később követtek az MLC-re (multi-level cell) épülő, olcsóbb darabok. Az SLC cellánként egyetlen bitet, míg az MLC cellánként kettőt tárol. Mivel az SLC adott területen kevesebb adatot képes eltárolni, így az gyorsabb is, mert a cella értékének megállapítása kevesebb időt vesz igénybe, ráadásul emellett élettartama is hosszabb, mint az MLC-é. Ennek az az oka, hogy egyetlen bithez (0, 1) csupán két feszültségi jellemző társul (alacsony és magas), melyek meghatározása jóval könnyebb, ezzel együtt pedig gyorsabb. Az MLC összesen két bitjéhez (00, 01, 10, 11) már összesen négy érték szükséges, azaz az adott intervallumot négy részre kell osztani, ergo pontosabb, többlépcsős feszültségek szükségesek a tárolt bitek állapotának meghatározásához.

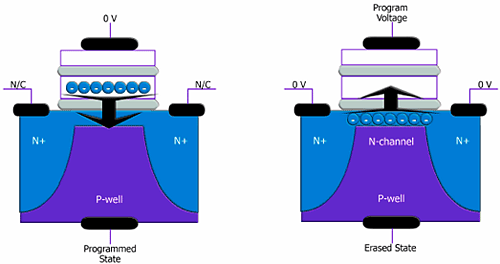

A továbbiak megértéséhez a fenti kis rajzon keresztül próbálunk mankót nyújtani, ahol elsősorban a nyilak szárai által keresztezett szürke csíkra kell fókuszálni. A nagyjából mindössze 10 nanométer vastagságú szilíciumdioxid réteg minden egyes programozási ciklussal veszít a képességeiből, a kötések lazulni kezdenek, amitől az elektronok idővel benn rekedhetnek. Ezzel a szilíciumdioxid töltése lassan megváltozik, ennek pedig egyenes következménye, hogy a bitek programozáshoz szükséges feszültségek határai eltolódnak. Ezt követően a cellák törléséhez már nagyobb feszültségre lesz szükség, ami csak további olaj a tűzre. A folyamat legvégén óhatatlan lesz az adott cella használatának mellőzése, azaz teljes kizárása.

A TLC (triple-level cell) még tovább megy, ugyanis egy ilyen típusú cella már három bitet tud tárolni, így például az SLC-hez képest egységnyi területen megtriplázza az elérhető tárkapacitást, míg az MLC-hez viszonyítva 50%-kal több adatot képes eltárolni. A feljebb vázolt sémát követi a TLC: a cellában helyet kapott három bitnek kombinálva összesen nyolc különböző állapota lehet, melyek mindegyikéhez egy-egy feszültség tartozik: 000, 001, 010, 100, 011, 101, 110, 111.

Mivel a feszültségtartomány fix, így azt ebben az esetben még kisebb szeletekre kell darabolni, ami még pontosabb értékeket kíván meg a tökéletes programozáshoz. Ebből következik, hogy az adott cella elhasználódása még korábban bekövetkezhet, ugyanis kisebb a nyolc feszültségtartomány közötti terület, ahova a szilíciumdioxid réteg "kopásának" következtében még hiba nélkül ki tud "futni" a vezérlés. Ezen felül, ha egy cella 3 bitnyi adatot tárol, akkor a programozási műveletek is gyakoribbak lesznek benne, hisz egyetlen bit módosításához (pl.: 000->001) is ugyanazt az műveletet igényli, mintha mindhárom módosításra kerülne (pl.: 010->101).

| NAND típus | SLC | MLC | TLC |

| Cellánkénti bitek száma | 1 | 2 | 3 |

|---|---|---|---|

| Max. programozási ciklus | 100 000 | 3000 | 1000 |

| Olvasási idő | 25 µs | 50 µs | 75 µs |

| Írási idő | 200-300 µs | 600-1200 µs | 900-1600 µs |

| Törlési idő | 1,5-2 ms | 2-3 ms | 4,5-5 ms |

A fenti táblázatból jól kivehető, hogy a TLC az MLC-hez képest nagyjából harmadannyi programozási (írás/törlés) ciklust képes elviselni. Ezen felül a különböző műveletek elvégzéséhez szükséges idő is tovább nőtt, ami elsőre szintén nem hangzik túl jól. Egyébiránt ez utóbbi szintén növekedhet egy szimpla csíkszélesség-csökkentéssel is. Erre jó példát nyújtanak az Intel által korábban publikált adatok, ugyanis 34 nanométerről 25-re ugorva az írási késleltetés az elődhöz képest 900 µs-ról 1200 µs-ra emelkedett, míg egy teljes blokk törlési késleltetése 2 µs-ról 3 µs-ra nőtt az MLC lapkák esetében.

Egy szó mint száz, a TLC egyetlen pozitív tulajdonsága az egységnyi területre eső tárkapacitás növelése. Ezt kétféle formában hasznosíthatják a gyártók: azonos területen nagyobb tárkapacitás, vagy azonos kapacitás kisebb területen. Mindkettő a csíkszélesség-csökkentéshez hasonlóan olcsóbb előállítást tesz lehetővé, melynek mértéke az MLC-hez képest nagyjából 30-40% közé tehető. Fontos megemlíteni, hogy a megoldás korántsem újkeletű, hisz egyes pendrive-okban, memóriakártyákon vagy hordozható médialejátszókban már régóta ott lapul a helytakarékosabb, cellánkénti 3 bit. Utóbbiakkal szemben az SSD-k világába a közelmúltig bezárólag nem szivárgott be a TLC, amit elsőként a Samsung elégelt meg.

A cikk még nem ért véget, kérlek, lapozz!