Árharc

Az SSD-k legdrágább komponense kétségkívül a NAND chip. Például egy 19 nanométeres gyártástechnológiával készített, 64 gigabit (azaz 8 GB) kapacitású lapka 94 mm² területű, amiből egy 64 GB-os SSD-be összesen nyolc darab kell. Ebből könnyen kiszámíthatjuk, hogy az említett, ráadásul manapság már meglehetősen kicsinek számító meghajtó NAND chipjeihez 752 mm² szilícium szükséges, mely területen majdnem kétszer elférne az NVIDIA legújabb csúcs Maxwell GPU-ja, a GM204. Természetesen egy NAND lapka jóval egyszerűbb felépítésű, mint egy GPU vagy CPU, ergo az előállítása azonos területtel számolva olcsóbb, hisz a gyártás folyamán kevesebb és egyszerűbb folyamatokon kell átessen az ostya (wafer), de pusztán az alapanyagot tekintve nagyjából összevethetőek a kiinduló költségek.

Azonos kapacitás kisebb területen [+]

Míg a processzoroknál a lapkához szükséges szilícium mennyiségének csökkentése mellett a fogyasztás (szivárgási áram) mérséklése és/vagy az órajel (a tranzisztorok teljesítményének) növelése a fő cél, addig a NAND-ok esetében a meglehetősen nagy szilíciumszükséglet okán a cella-, illetve bitsűrűség növelése a legfontosabb feladat. Aktuálisan mindig az a gyártó van igazán nyeregben, aki a legolcsóbban képes adott kapacitású lapka előállítására, hisz így nagyobb profittal tudja értékesíteni termékét és/vagy konkurenseinél olcsóbban kerülhet piacra SSD-je, ami így a felhasználók számára vonzóbb választás lehet, illetve még szélesebb vásárlóréteget érhet el.

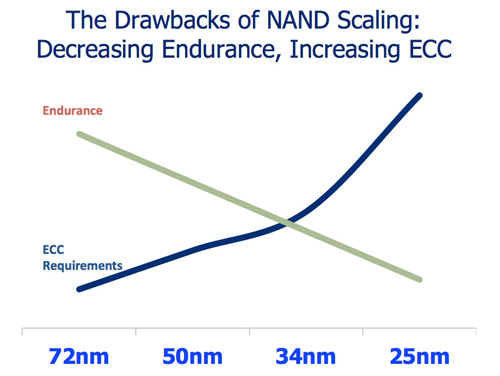

Emiatt az elmúlt években nagyon komolyan vették a csíkszélesség minél rohamosabb léptékben való csökkentését; míg 3-4 éve a 34 nanométeres lapkák voltak többségben, addig ma már a kritikus 20 nanométer alá ment az összes vállalat.

Igen ám, de ilyen alacsony csíkszélesség esetében már vészesen megnő az egyes cellák töltése közti áthallás (interferencia), ami egyre inkább igénybe veszi a meghajtó vezérlőjének ECC és DSP képességét, ez pedig amellett, hogy megnehezíti a mérnökök dolgát, negatív hatással van az átviteli tempóra. Fizikai törvényszerűség, hogy minél kisebb egy cella, annál kevesebb elektron fér el benne. Az aktuálisan legkisebb csíkszélességen készülő cellákban nagyjából 20 elektron kaphat helyet, ami a többszintes (MLC, TLC) cellák esetén eloszlik az egyes bitek között. Amennyiben az egyetlen bithez tartozó összes elektron kiszabadul a cellából, úgy az adott cella használhatatlanná válik.

Az egységnyi területre jutó kapacitás növelésére vonatkozó kutatások évekre, sőt inkább már évtizedekre nyúlnak vissza, többek között az egyetlen cellában tárolt adatmennyiség növelése is erre hivatott. Az MLC (2 bit) és a TLC (3 bit) típusú NAND-ok erre szolgálnak, melyek közül az utóbbiból egyelőre csak a Samsungtól láthattunk kereskedelmi forgalomba került terméket. Az SLC, MLC, TLC témát korábban már kiveséztük. Röviden összefoglalva, az MLC az SLC-hez képest teoretikusan 100%-kal növelte az adatsűrűséget, míg a TLC az MLC-hez képest 50%-kal. Ezen megoldások hátulütője, hogy a több bit tárolására képes cellák kevesebb programozási ciklust képesek elviselni, ugyanakkor a gyártók ezt különféle fejlett vezérlési metódusokka jól kezelik, ezzel pedig a valós elhasználódás mértékét kordában tudják tartani.

A Samsung csíkszélesség terén jelenleg valahol 19-16 nm környékén jár, illetve ahogy említettük, már ellőtték a TLC, vagy ahogy ők hívják a 3-bit MLC lehetőségét is, így lassan szükség volt egy olyan új technológia élesben való bevetésére, amivel viszonylag könnyen és gyorsan tudják még tovább növelni a cellasűrűséget.

A cikk még nem ért véget, kérlek, lapozz!