Az ARM még a 2018-as esztendő őszén leplezte le a Neoverse termékcsaládot, amelybe első körben az N1 és az E1 platformok kerültek, míg az előző év őszén a V1 és az N2 platformok lettek leleplezve. Utóbbiakról beszélt bővebben a vállalat az ARM Tech Day 2021 rendezvényen, és mellettük még bemutatkozott a CMN-700 is, ami a magok közötti összeköttetésért felel.

A V1 platform elsődlegesen a magas egy szálon mérhető teljesítményre fókuszál, és 7 vagy 5 nm-es node-ra tervezhető, méghozzá PCI Express 5.0, DDR5, HBM3, CXL és CCIX 1.1 támogatással. A dizájn a Zeus kódnevű magra épít, amelynél az ARM szerint 50%-kal növelik az IPC-t az N1-hez viszonyítva. Ez azonban nem mond el mindent a fejlesztésről, mivel a fókuszt leginkább a HPC-piac jelenti, és emiatt érkezik az SVE, azaz Scalable Vector Extension, méghozzá két darab 256 bites SIMD motor formájában. Ezek a feldolgozók egyrészt támogatnak négy 128 bites NEON/FP operációt, de a fő előnyük tényleg az új, SVE-re direkten felkészített kódoknál látszik majd meg, mivel azokkal könnyebben skálázható a hardver.

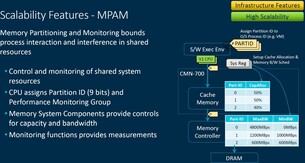

A Neoverse V1 az ARMv8.4-es architektúrát használja, de bizonyos ARMv8.5 és ARMv8.6 architektúrákba tervezett képességek vissza vannak portolva. Itt gépi tanulásra, ezen belül is a tréning szakaszra koncentráló funkciókról van szó, így például nem hiányzik a fejlesztésből a bfloat16 támogatása sem. A dizájn támogatja még az MPAM, azaz a Memory Partitioning and Monitoring funkciót, amivel menedzselhető az elérhető memória-sávszélesség, illetve ott lesz a CBusy, amivel a rendszeren belüli torlódások kezelhetők. Utóbbi az extrém mértékben skálázott konfigurációknál lesz kiemelten hasznos.

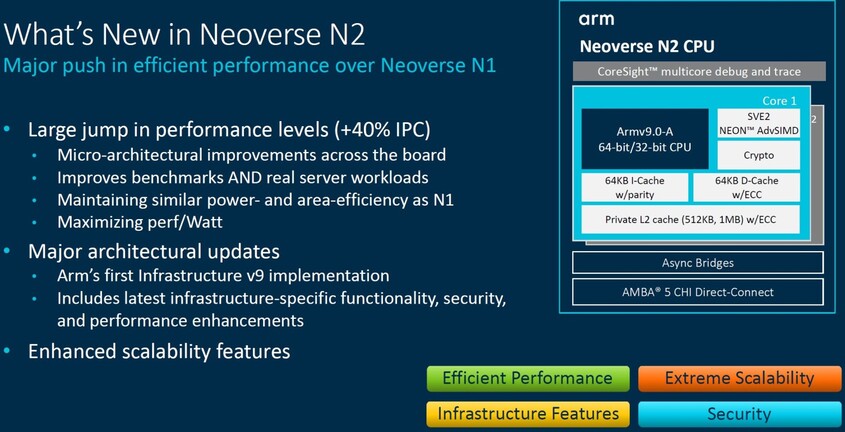

Az ARM másik fejlesztése az N2 platform, ami leginkább az adatközpontokat fogja támadni, és ez már csak 5 nm-re készül, illetve a PCI Express 5.0 és a DDR5 is alap, továbbá opcióként elérhető a HBM3, a CCIX 2.0 és a CXL 2.0. A dizájn az újabb Perseus magra épít, ami már egy biztonsági szempontok alapján is kigyúrt ARMv9-es architektúrát kamatoztatja. Ennek hála elérhető lesz a CCA, az MTE, a bfloat16 és az SVE2 , utóbbi esetében viszont két darab 128 bites SIMD motor lesz beépítve. Itt rögtön látszik, hogy a Neoverse N2 a V1-gyel ellentétben nem tekinti kritikusnak az egy szálon biztosított teljesítményt, inkább a skálázhatóság kerül a középpontba.

Az ARM szerint 40%-kal növelik az IPC-t az N1-hez viszonyítva, ami nem akkora előrelépés, mint a V1-nél, illetve a SIMD motorok szelessége is visszafogott, viszont egy tokozásra vetítve 128-nál is több szállal lehet majd számolni, ami az adatközpontokban, vagyis a célpiacon nagyon hasznos.

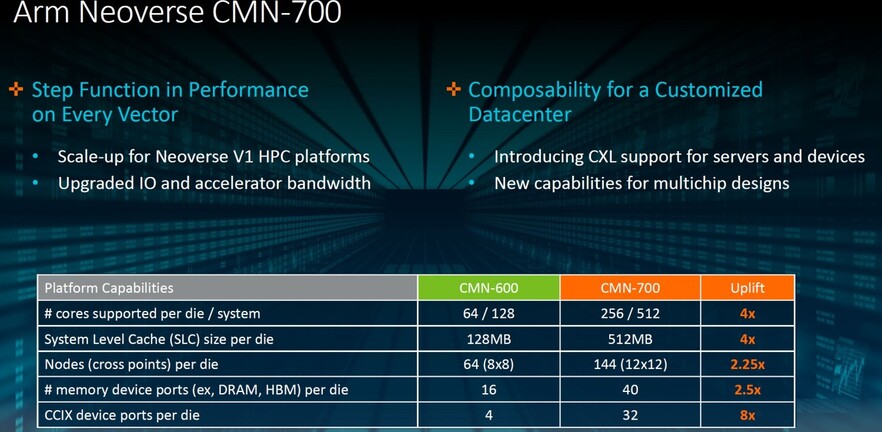

A fenti két fejlesztésen túl van egy olyan komponens, ami nélkül nem lehetne mit kezdeni a szerverpiacon. A processzormagokat ugyanis össze kell kötni, ami triviálisnak tűnik, de valójában cseppet sem egyszerű egy tokozáson belül ennyi magot hatékonyan kezelni, az egyes lapkák közötti kommunikációt biztosítani pedig pláne nem könnyű. Az ARM a problémára a CMN-700-at veti be, ami egy koherens, halós topológiát alkalmazó összeköttetést vezérlő rendszer.

Ez a fejlesztés a Neoverse V1 és N2 platformokhoz is bevethető. Ennek az oka, hogy a V1 és az N2 esetében is úgynevezett tile-okkal kell tervezni a lapkán belüli skálázást, és egy ilyen tile-ban két ARM Zeus vagy Perseus mag kap helyet, természetesen a platformtól függően. A magokon belül kiválasztható az L2 gyorsítótár kapacitás, ami lehet 0,5 vagy 1 MB, és a tile-okon belül pedig kialakítható a rendszerszintű gyorsítótár egy szelete. Ez persze még nem minden, hiszen memóriavezérlő, a CXL-t támogató PCI Express vezérlő, illetve a CCIX összeköttetések is a CMN-700-hoz vannak kapcsolva, illetve a különböző egyéb, adott lapkán belüli részegységek is. A tokozások közötti összekapcsolást egyébként a CCIX biztosítja.

A CMN-700-zal egy lapkán belül maximum 256 mag, 512 MB-nyi rendszerszintű gyorsítótár, 32 darab CCIX, illetve 40 darab memóriaport lehet. Ezek egyébként csak a végletek, az említett összeköttetés nagymértékben konfigurálható. Többek között egy tokozáson belül is bevethető két ugyanolyan vagy több eltérő felépítésű lapka. A lehetőségeket itt alapvetően a licencelő határozza meg.

Az ARM szerint a Neoverse V1 és N2 dizájnok leghamarabb 2022-ben érkezhetnek.