Az Intel még az elmúlt hónap elején jelentette be az új Xeonokat, pontosabban adtak egy átfogó képet, hogy miképp változik meg a nevezéktan, és azt is meg lehetett tudni, hogy mik az újdonságok, de a konkrét modellekkel még nem állt elő a cég. Ezt ezúttal sem tették meg, ugyanakkor bejelentették, hogy az új Skylake-X/SP kódnevű fejlesztések már új összeköttetést használnak a magok között.

A korábbi generációkban az Intel erre gyűrűs buszokat használt, amely gyors és alacsony késleltetésűnek bizonyult, de igazán csak 12 mag összeköttetéséig működött. Emiatt nem is mentek egyetlen processzorral sem fölé, így a 12-nél több magot tartalmazó lapkákat úgy építették fel, hogy több részre bontották a belső összeköttetést. Ilyen volt például a Broadwell-EX, amelynél a 24 mag valójában két darab tizenkét magot tartalmazó, gyűrűs buszokat használó blokkból állt, és ezek voltak két-két extra megállón keresztül összekötve.

Ezt lehetett volna tovább skálázni, hiszen akár több blokk is beépíthető, de nem célszerű ebbe az irányba fejleszteni. Ennél ugyanis az Intel már alkalmazott egy jobb rendszert a Knights Corner kódnevű fejlesztésben, ahol a 36 darab kétmagos processzormodult hálós topológiával sikerült összekötni.

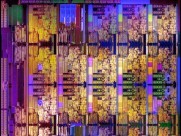

Gyakorlatilag a Skylake-X/SP generáció ezt másolta le, így ezekben a lapkákban a magok és a kapcsolódó komponensek egyedi megállókat kaptak. Maguk a részegységek sakktáblához hasonló módon vannak egymás mellé helyezve, és minden komponens össze van kötve az adott sorban és adott oszlopban található társával. Az adatmozgásról az Intel nem beszélt bővebben, de szinte biztos, hogy ugyanúgy működik a rendszer, mint a Knights Corner kódnevű lapkán, vagyis az egyes szomszédos megállóknál az adatmozgás egy órajelbe kerül. A célzott komponenst szervezet logika alapján érik el, az adat így először vertikálisan mozogva jut el a megfelelő sorba, majd horizontálisan a megfelelő oszlopba és ezen belül a megfelelő részegységbe.

Ezzel a megoldással a lapkán belül minden részegységhez viszonylag gyorsan eljuttatható az a kért információ, így például nem lesz azzal probléma, hogy már a magon belül is két blokkra van osztva a rendszer, amikor is az adatmozgás kirívó esetékben magas késleltetést eredményezhet. Ez ellen persze lehet küzdeni szoftveresen és manapság ezt meg is teszik a programfejlesztők, de a hálós topológiával alapból széles spektrumon skálázható a lapka az esetleges szoftveres trükközések nélkül. Persze a hálós topológia a gyakorlatban az átlagos késleltetést egy picit megnöveli, mivel a keresztirányú mozogásokat is le kell kezelni, de ez bőven elfogadható kompromisszum az előnyök mellett.

Az Intel egyébként a Skylake-X/SP generációhoz három lapkát fejleszt, ami cseppet sem költséghatékony, de érdemes ennyi verziót tervezni, ugyanis a 28 maggal rendelkező, XCC dizájn 700-800 mm² közötti kiterjedéssel bír, amit nagyon drága gyártani. Emiatt lesz egy 500-550 mm² közötti HCC verzió, amelyben csak 18 mag lesz, illetve a 350 mm² körüli LCC változat a maga 10 magjával a legkisebb.