Az AMD az első Athlon 64 tervezésénél úgy döntött, hogy az x86-os processzorgyártók között elsőként beveti a CPU-ba integrált memóriavezérlőt (IMC). Ezzel gyakorlatilag az addigi alaplapok északi-hídjában található memóriavezérlő átkerült a CPU-t tartalmazó szilícium lapkába.

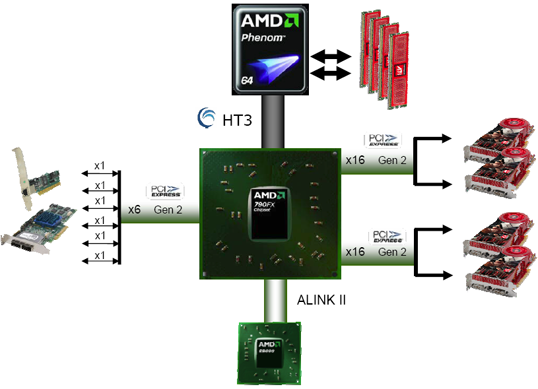

Az alaplapi északi-hídban a memóriavezérlő kiollózása után még maradtak különböző létfontosságú egységek: AGP, PCI Express vezérlő, videóvezérlő (IGP/GPU), stb. Illetve a déli-hídról se feledkezzünk meg, ami az USB, hang, PCI, PATA, SATA, stb. vezérlésekért felelős. Kellett valami, ami kellően rugalmas és az FSB-t helyettesítve összeköti a chipkészletet és a processzort, ezzel megvalósítva a nélkülözhetetlen CPU<-->chipkészlet kommunikációt. Így született meg és vette át a Front Side Bus szerepét a HyperTransport busz.

A szabvány illetve a technológia megalkotása felett a HyperTransport konzorcium bábáskodik, melynek többek között tagja az AMD, az Apple, a Broadcom, a Cisco, a Xilinx, valamint az NVIDIA is. A szabvány jelenleg a 3.1-es verzióját tapossa, mellyel egy darab kétrányú (full duplex, azaz 16 bit fel és 16 bit le) 16 bites, 3,2 GHz-es kapcsolat esetében 25,6 GB/s maximális sávszélességű pont-pont kapcsolat hozható létre. Jó tudni, hogy a kapcsolat DDR, azaz (Double Data Rate), egy órajelciklus alatt egyidejűleg két átvitelt képes végrehajtani. E mellett olyan esettel is találkozhatunk, ahol az átvitel sebességét MT/s (megatransfers per second) vagy GT/s (gigatransfers per second) mértékegységgel jelölik. 1 MT/s egymillió átvitelt jelent másodpercenként. (4000MT/s = 4GT/s)

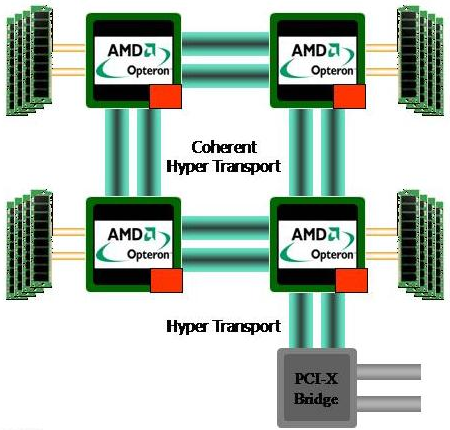

Ugyan a legtöbben az AMD-alapú asztali számítógépekből ismerhetik a HyperTransport-ot, ennek ellenére ma már sokkal nagyobb szerepet tölt be a szerverek világában. Az Opteron processzorok esetében az egyes CPU-k közötti kapcsolatért is a HyperTransport felel, ráadásul ebben az esteben már koherens, azaz nem csak egyszerű, a processzor és valamely alaplapi híd közötti I/O kapcsolatról beszélhetünk. Koherens kapcsolat képes kettő vagy több processzoros rendszerekben az egyes CPU-k összekötésére, miközben a cache konzisztencia is biztosítva van. Az AMD ezt a saját fejlesztésű rendszert NUMA-nak (Non-Uniform Memory Architecture) hívja. A megoldás lényege, hogy minden egyes processzor saját memóriával rendelkezik, melyhez az integrált memóriavezérlő segítségével villámgyorsan hozzáfér. Emellett a koherens HyperTransport kapcsolat segítségével a rendszer bármelyik pocesszora képes elérni a másik memóriáját. Ez természetesen valamivel lassabban, magasabb késleltetés mellett megy végbe, ugyanakkor egy jól megtervezett rendszerben ilyen műveletekre relatíve ritkán van szükség, mivel optimális esetben az egyes processzorok elsősorban saját memóriájukat használják.